## CORRIGÉ TYPE DE L'INTERROGATION

Samedi 07 Mai 2022 – Durée 1h15

**Exercice 1.** (4.5 Pts - 35 min).

I. 1. Il faut 4 sorties pour réaliser ce circuit. 0.5 Pt

2. La table de vérité correspondant à ce circuit (1 pt)

| $X_1$ | $X_0$ | $Y_3$ | $Y_2$ | $Y_1$ | $Y_0$ |

|-------|-------|-------|-------|-------|-------|

| 0     | 0     | 0     | 0     | 0     | 0     |

| 0     | 1     | 0     | 0     | 0     | 1     |

| 1     | 0     | 0     | 1     | 0     | 0     |

| 1     | 1     | 1     | 0     | 0     | 1     |

3. Les expressions simplifiées de ce circuit. (1 pt)

$$Y_3 = X_1 X_0 \quad \text{0.25 Pt}$$

$$Y_2 = X_1 \overline{X_0} \quad \text{0.25 Pt}$$

$$Y_1 = 0 \quad \text{0.25 Pt}$$

$$Y_0 = \overline{X_1} X_0 + X_1 X_0 = X_0 \quad \text{0.25 Pt}$$

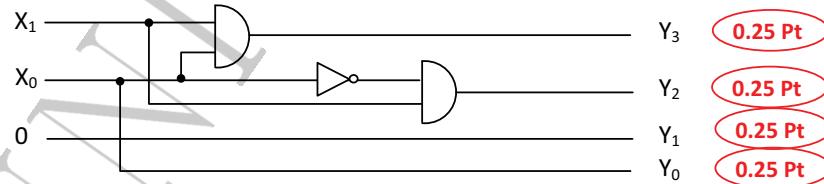

4. Le schéma logique de ce circuit. (1 pt)

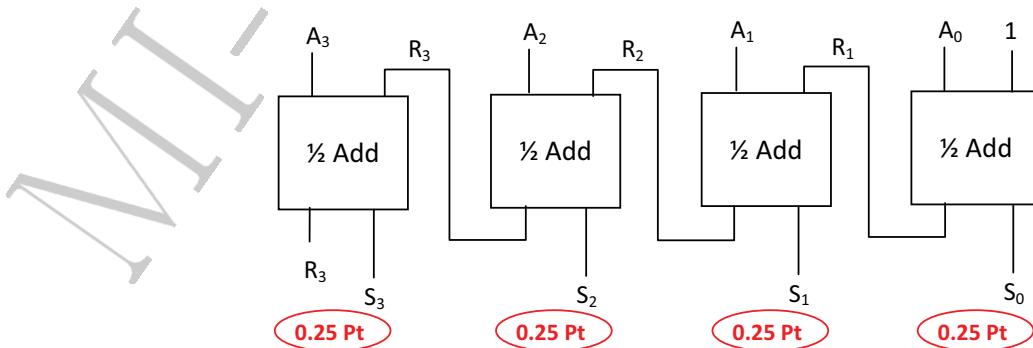

II. Le schéma de câblage d'un incrémenteur à quatre bits. (1 pt)

**Exercice 2. (5.5 Pts - 40 min).**

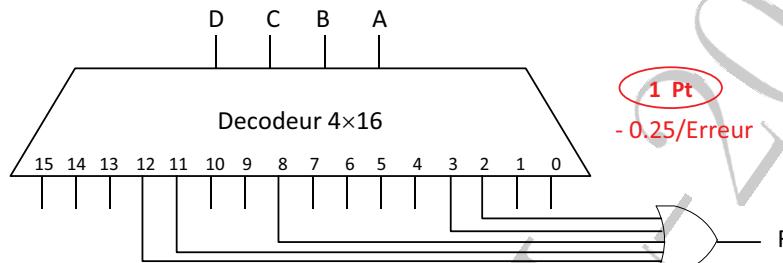

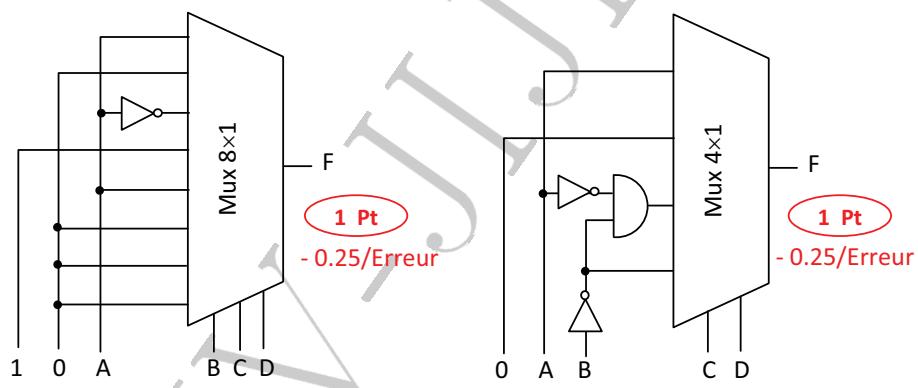

I. Soit la fonction logique suivante :

$$F(A, B, C, D) = A \cdot \overline{C} \cdot \overline{D} + \overline{A} \cdot \overline{B} \cdot C + \overline{B} \cdot C \cdot D$$

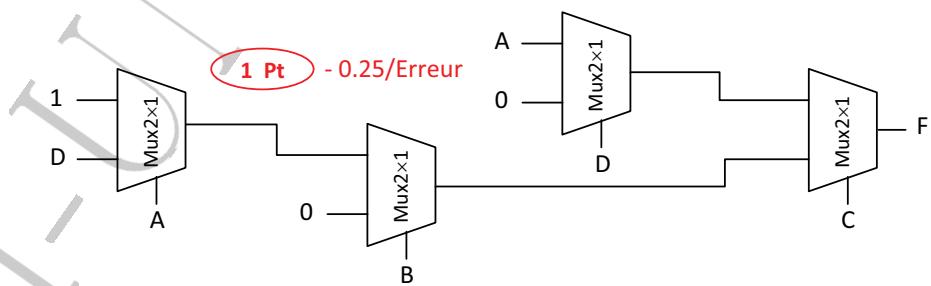

1. Réalisation de cette fonction en utilisant un décodeur  $4 \times 16$ . (1 pt)2. et 3. Réalisation de cette fonction à l'aide d'un multiplexeur  $8 \times 1$  et à l'aide d'un multiplexeur  $4 \times 1$ . (1 pt)4. Réalisation de cette fonction en utilisant uniquement des multiplexeurs  $2 \times 1$  (le minimum de multiplexeurs). (1 pt)II. L'expression logique de la sortie  $S$  est :  $S = (\overline{A} \oplus \overline{B}) \cdot (\overline{C} \oplus \overline{D})$  (1.5 Pt)