# Support de Cours

# STRUCTURE MACHINE

## Cours avec exemples explicatifs

Destiné aux étudiants en première année licence (LMD)

Mathématiques et informatique (MI)

2020

2021

Elaboré par :

**Dr. BOULAICHE AMMAR**

Maitre de conférences - Département d'informatique

Faculté des sciences exactes et informatique

Université de Jijel

# Avant-propos

Ce support de cours représente le fruit d'un enseignement délivré depuis de nombreuses années aux étudiants en graduation. Il est destiné principalement aux étudiants de la première année tronc commun Mathématiques et Informatique (MI) de l'université de Jijel. Mais il peut également être utilisé par toute personne ayant besoin d'acquérir les notions de base des systèmes de numération, de l'algèbre de Boole et des circuits numériques.

Le contenu de ce support recouvre le programme du module structure machine I et II selon le dernier syllabus délivré par le ministère de l'enseignement supérieur et de la recherche scientifique. Les chapitres de ce support sont présentés d'une façon simple et facile, dans lesquels l'étudiant trouvera une partie cours suffisamment détaillée expliquant les notions fondamentales abordées avec des exemples permettant d'appliquer directement ces notions.

Pour terminer, nous espérons que le présent support répondra aux attentes des étudiants quelque soit leur niveau, et qu'il les aidera à progresser dans leurs études et les mettra sur la voie du succès dans leur cursus.

# Table des matières

|                                                                                          |           |

|------------------------------------------------------------------------------------------|-----------|

| <b>Avant-propos</b>                                                                      | <b>I</b>  |

| <b>1 Représentation des données</b>                                                      | <b>1</b>  |

| 1.1 Introduction . . . . .                                                               | 1         |

| 1.2 Changements de bases . . . . .                                                       | 1         |

| 1.2.1 Conversion du décimal en une base $b$ quelconque . . . . .                         | 2         |

| 1.2.2 Conversion d'une base $b$ quelconque en décimal . . . . .                          | 3         |

| 1.2.3 Conversion d'une base $b = 2^n$ quelconque en binaire . . . . .                    | 3         |

| 1.2.4 Conversion du binaire en une base $b = 2^n$ quelconque . . . . .                   | 3         |

| 1.2.5 Conversion d'une base $b_1$ en une base $b_2$ ( $b_1 \neq b_2 \neq 10$ ) . . . . . | 3         |

| 1.3 Opérations arithmétiques en base $b$ quelconque . . . . .                            | 4         |

| 1.3.1 Addition . . . . .                                                                 | 4         |

| 1.3.2 Soustraction . . . . .                                                             | 4         |

| 1.3.3 Multiplication . . . . .                                                           | 5         |

| 1.3.4 Division . . . . .                                                                 | 5         |

| 1.4 Représentation des données . . . . .                                                 | 5         |

| 1.4.1 Représentation des nombres entiers . . . . .                                       | 6         |

| 1.4.1.1 Entiers naturels . . . . .                                                       | 6         |

| 1.4.1.2 Entiers relatifs . . . . .                                                       | 6         |

| 1.4.2 Représentation des nombres réels . . . . .                                         | 7         |

| 1.4.2.1 Représentation en virgule fixe . . . . .                                         | 7         |

| 1.4.2.2 Représentation en virgule flottante . . . . .                                    | 8         |

| 1.4.2.2.1 Passage du décimal vers la virgule flottante .                                 | 8         |

| 1.4.2.2.2 Passage de la virgule flottante vers le décimal                                | 9         |

| 1.4.3 Représentation des données non numériques (textes) . . . . .                       | 9         |

| 1.4.3.1 Code ASCII . . . . .                                                             | 10        |

| 1.4.3.2 Code ASCII étendu . . . . .                                                      | 12        |

| 1.4.3.3 Encodage UNICODE . . . . .                                                       | 12        |

| 1.4.4 Autres codes particuliers . . . . .                                                | 13        |

| 1.4.4.1 Code BCD . . . . .                                                               | 13        |

| 1.4.4.1.1 Addition en BCD . . . . .                                                      | 13        |

| 1.4.4.1.2 Soustraction en BCD . . . . .                                                  | 13        |

| 1.4.4.2 Code Gray . . . . .                                                              | 14        |

| 1.4.4.2.1 Transcodage Binaire - Gray . . . . .                                           | 14        |

| 1.4.4.2.2 Transcodage Gray - Binaire . . . . .                                           | 14        |

| 1.4.4.3 Codes détecteurs d'erreur . . . . .                                              | 15        |

| <b>2 Algèbre de Boole</b>                                                                | <b>16</b> |

| 2.1 Introduction . . . . .                                                               | 16        |

| 2.2 Définition de l'algèbre de Boole . . . . .                                           | 16        |

|           |                                                                     |           |

|-----------|---------------------------------------------------------------------|-----------|

| 2.3       | Théorèmes fondamentaux de l'algèbre de Boole . . . . .              | 17        |

| 2.4       | Fonctions de base de l'algèbre de Boole . . . . .                   | 17        |

| 2.5       | Représentation d'une fonction logique . . . . .                     | 18        |

| 2.5.1     | Table de vérité d'une fonction logique . . . . .                    | 18        |

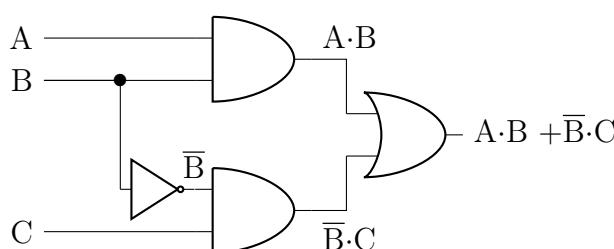

| 2.5.2     | Logigramme d'une fonction logique . . . . .                         | 18        |

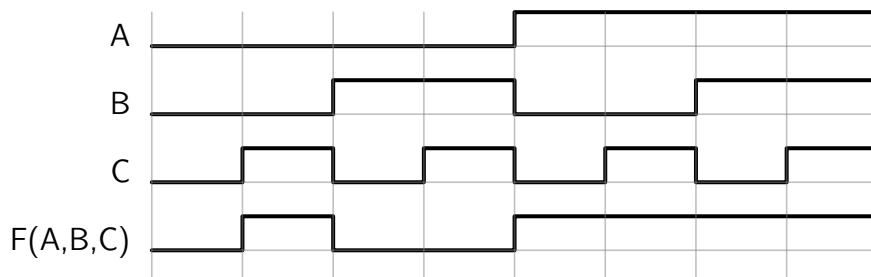

| 2.5.3     | Chronogramme d'une fonction logique . . . . .                       | 19        |

| 2.6       | Forme canonique d'une fonction logique . . . . .                    | 19        |

| 2.6.1     | Définitions . . . . .                                               | 19        |

| 2.6.2     | Mettre une fonction en première forme canonique . . . . .           | 20        |

| 2.6.2.1   | La méthode algébrique . . . . .                                     | 20        |

| 2.6.2.2   | La méthode de la table de vérité . . . . .                          | 20        |

| 2.6.3     | Mettre une fonction en deuxième forme canonique . . . . .           | 20        |

| 2.6.3.1   | La méthode algébrique . . . . .                                     | 21        |

| 2.6.3.2   | La méthode de la table de vérité . . . . .                          | 21        |

| 2.6.4     | Représentation décimale des deux formes canoniques . . . . .        | 21        |

| 2.6.5     | Fonctions logiques avec uniquement des portes NAND et NOR . . . . . | 22        |

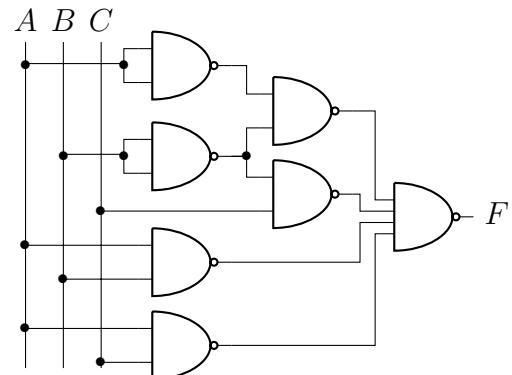

| 2.6.5.1   | Expression d'une fonction logique avec des portes NAND . . . . .    | 22        |

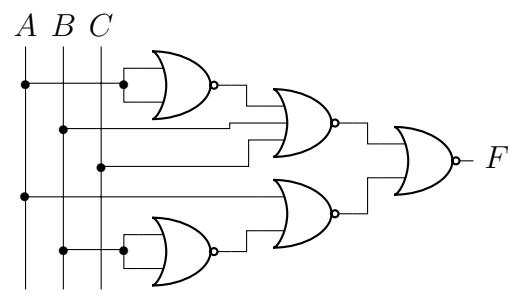

| 2.6.5.2   | Expression d'une fonction logique avec des portes NOR . . . . .     | 22        |

| 2.7       | Simplification des fonctions logiques . . . . .                     | 23        |

| 2.7.1     | Méthode algébrique . . . . .                                        | 23        |

| 2.7.2     | Méthode de karnaugh . . . . .                                       | 24        |

| 2.7.2.1   | Table de karnaugh . . . . .                                         | 24        |

| 2.7.2.1.1 | Caractéristiques de la table de karnaugh . . . . .                  | 24        |

| 2.7.2.1.2 | Table de Karnaugh à partir de la table de vérité . . . . .          | 24        |

| 2.7.2.1.3 | Table de Karnaugh à partir de la forme canonique . . . . .          | 25        |

| 2.7.2.2   | Méthode de simplification . . . . .                                 | 25        |

| 2.7.2.3   | Tables de karnaugh avec des valeurs inconnues . . . . .             | 25        |

| 2.7.2.4   | Tables de karnaugh à cinq variables . . . . .                       | 26        |

| 2.7.2.5   | Tables de karnaugh à six variables . . . . .                        | 27        |

| 2.7.3     | Méthode de Quine Mc Cluskey . . . . .                               | 28        |

| <b>3</b>  | <b>Circuits logiques combinatoires</b>                              | <b>30</b> |

| 3.1       | Introduction . . . . .                                              | 30        |

| 3.2       | Synthèse des systèmes combinatoires . . . . .                       | 30        |

| 3.3       | Synthèse des principaux circuits combinatoires . . . . .            | 31        |

| 3.3.1     | L'additionneur . . . . .                                            | 31        |

| 3.3.1.1   | Le semi-additionneur . . . . .                                      | 31        |

| 3.3.1.2   | L'additionneur complet . . . . .                                    | 31        |

| 3.3.1.3   | L'additionneur $n$ bits . . . . .                                   | 33        |

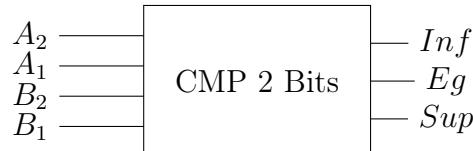

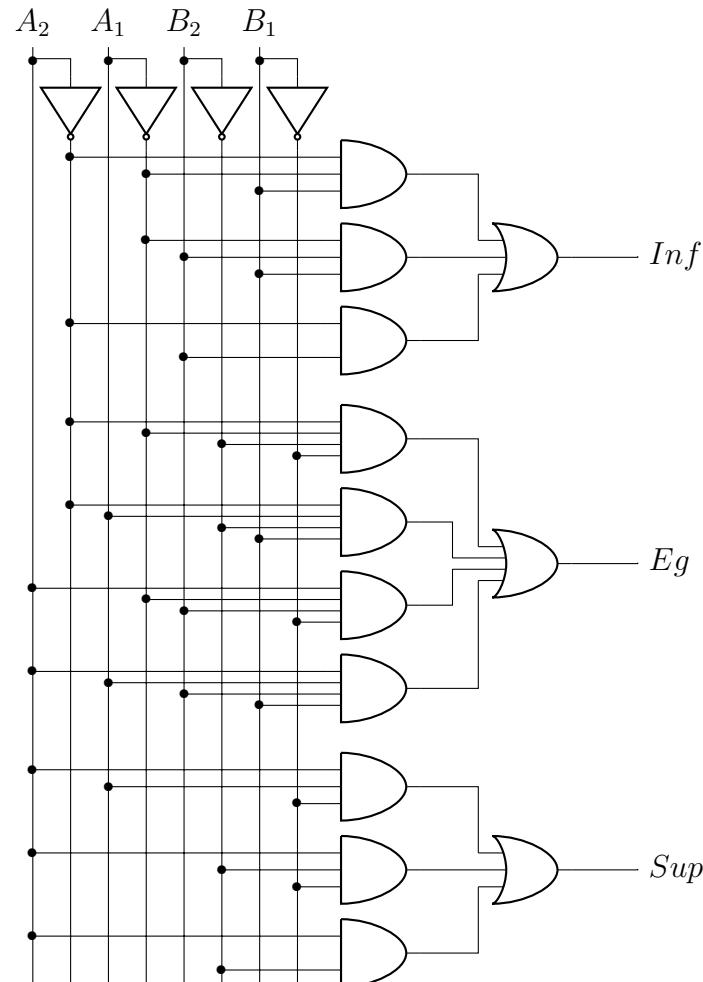

| 3.3.2     | Le comparateur 2 bits . . . . .                                     | 33        |

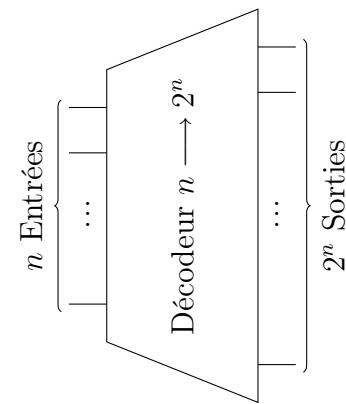

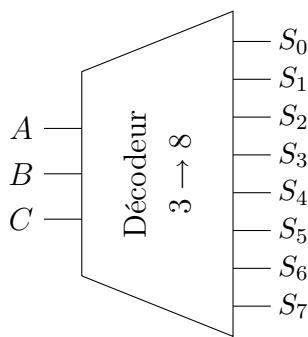

| 3.3.3     | Le décodeur . . . . .                                               | 35        |

| 3.3.4     | L'encodeur . . . . .                                                | 36        |

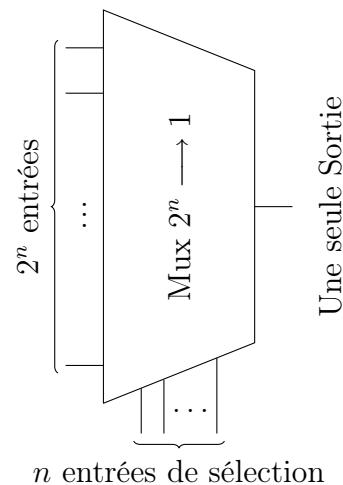

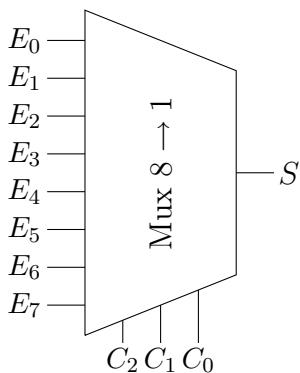

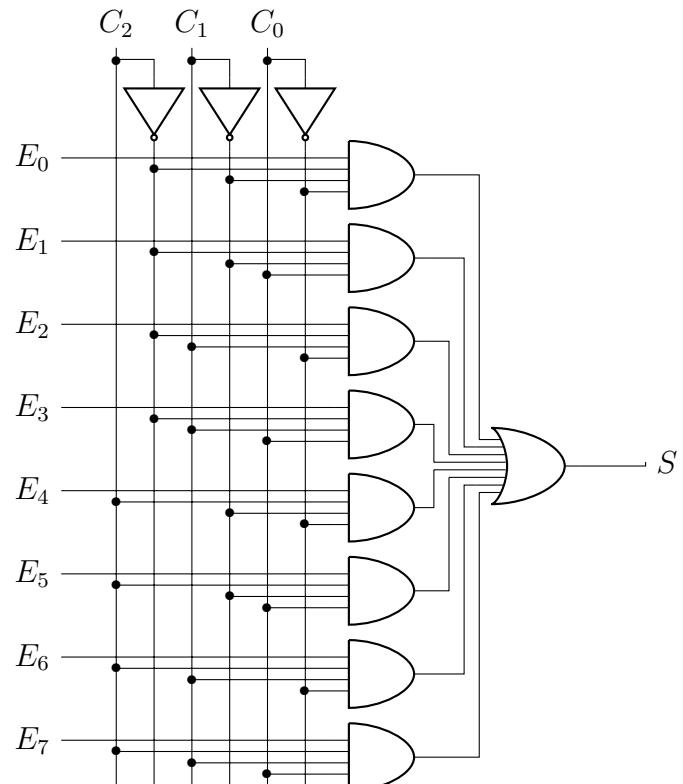

| 3.3.5     | Le multiplexeur . . . . .                                           | 36        |

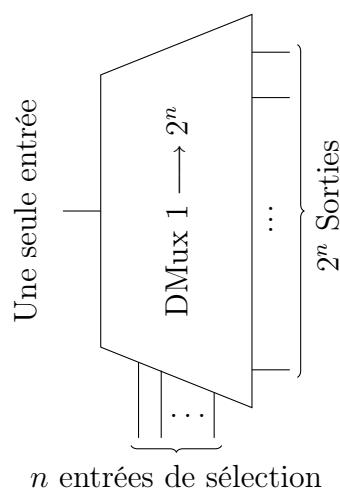

| 3.3.6     | Le démultiplexeur . . . . .                                         | 37        |

| 3.3.7     | Génération des fonctions logiques via des multiplexeurs . . . . .   | 38        |

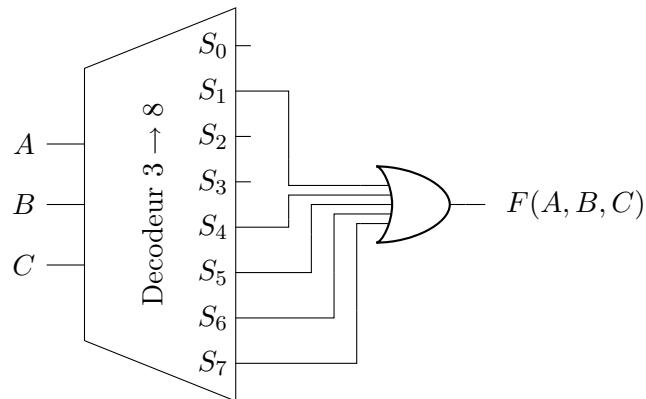

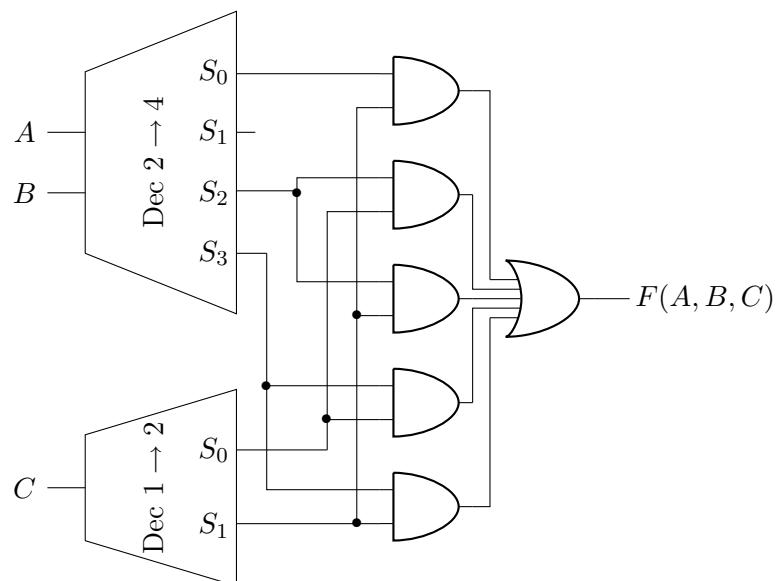

| 3.3.8     | Génération des fonctions logiques via des décodeurs . . . . .       | 39        |

---

|                                                                           |           |

|---------------------------------------------------------------------------|-----------|

| <b>4 Circuits logiques séquentiels</b>                                    | <b>41</b> |

| 4.1 Introduction . . . . .                                                | 41        |

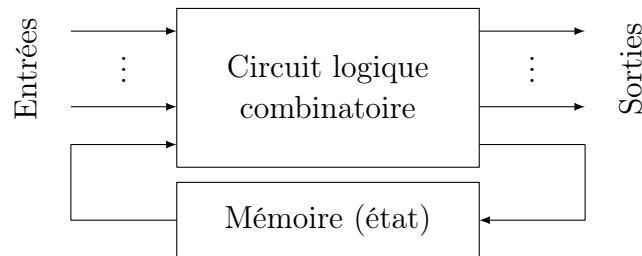

| 4.2 Modèles des circuits séquentiels . . . . .                            | 41        |

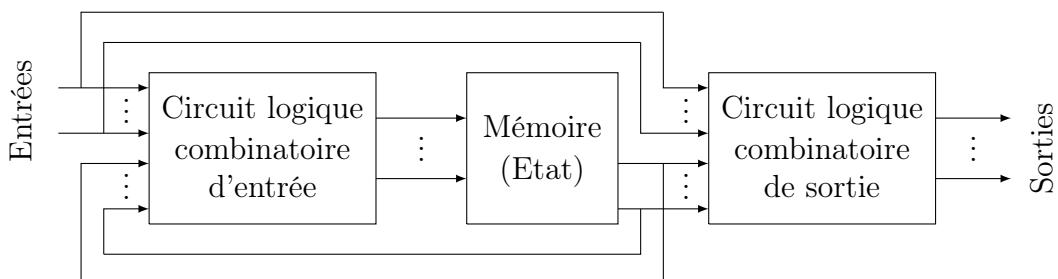

| 4.2.1 Machines de Mealy . . . . .                                         | 41        |

| 4.2.2 Machines de Moore . . . . .                                         | 42        |

| 4.3 Automates à états finis (graphes de transitions) . . . . .            | 42        |

| 4.3.1 Types de graphes de transitions . . . . .                           | 42        |

| 4.3.1.1 Graphes de Moore . . . . .                                        | 42        |

| 4.3.1.2 Graphes de Mealy . . . . .                                        | 43        |

| 4.3.2 Passage du graphe de Moore au graphe de Mealy . . . . .             | 43        |

| 4.3.3 Passage du graphe de Mealy au graphe de Moore . . . . .             | 44        |

| 4.4 Circuits séquentiels à base de bascules . . . . .                     | 44        |

| 4.4.1 Types de bascules . . . . .                                         | 44        |

| 4.4.1.1 Bascules asynchrones . . . . .                                    | 44        |

| 4.4.1.2 Bascules synchrones . . . . .                                     | 45        |

| 4.4.2 Bascules de base des circuits séquentiels . . . . .                 | 45        |

| 4.4.2.1 La bascule RS . . . . .                                           | 45        |

| 4.4.2.2 La bascule RSH . . . . .                                          | 46        |

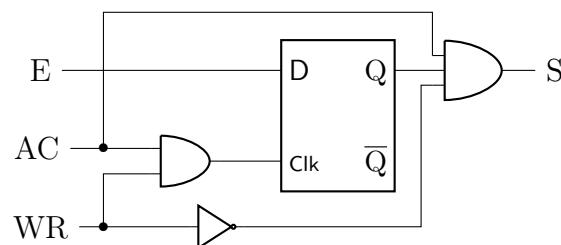

| 4.4.2.3 La bascule D . . . . .                                            | 48        |

| 4.4.2.4 La bascule JK . . . . .                                           | 48        |

| 4.4.2.5 La bascule T . . . . .                                            | 49        |

| 4.4.3 Analyse des circuits séquentiels à bascules . . . . .               | 50        |

| 4.4.4 Synthèse des circuits séquentiels à bascules . . . . .              | 51        |

| 4.5 Application des circuits séquentiels à bascules . . . . .             | 53        |

| 4.5.1 Les registres . . . . .                                             | 53        |

| 4.5.1.1 Définition . . . . .                                              | 53        |

| 4.5.1.2 Types de registres . . . . .                                      | 54        |

| 4.5.1.2.1 Registres à entrées parallèles et sorties parallèles            | 54        |

| 4.5.1.2.2 Registres à entrées parallèles et sorties série .               | 55        |

| 4.5.1.2.3 Registres à entrées série et sorties parallèles .               | 55        |

| 4.5.1.2.4 Registres à entrées série et sorties série . . .                | 56        |

| 4.5.2 Les compteurs . . . . .                                             | 57        |

| 4.5.2.1 Les compteurs asynchrones . . . . .                               | 57        |

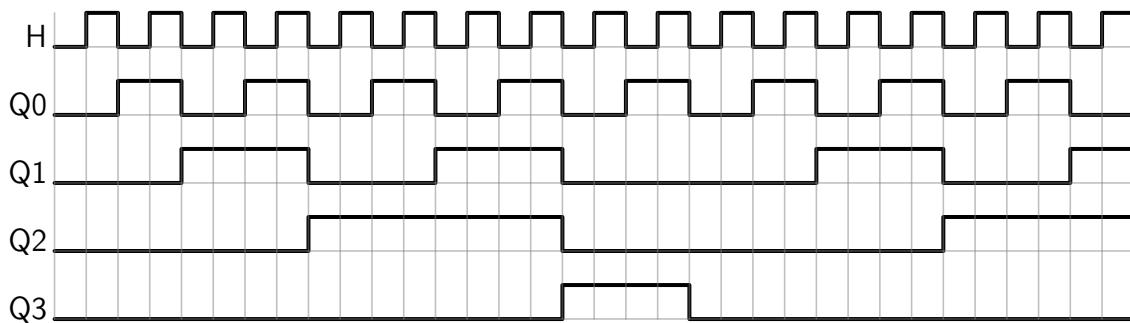

| 4.5.2.1.1 Compteurs asynchrones à cycle complet . . . .                   | 57        |

| 4.5.2.1.2 Compteurs asynchrones à cycle incomplet . .                     | 58        |

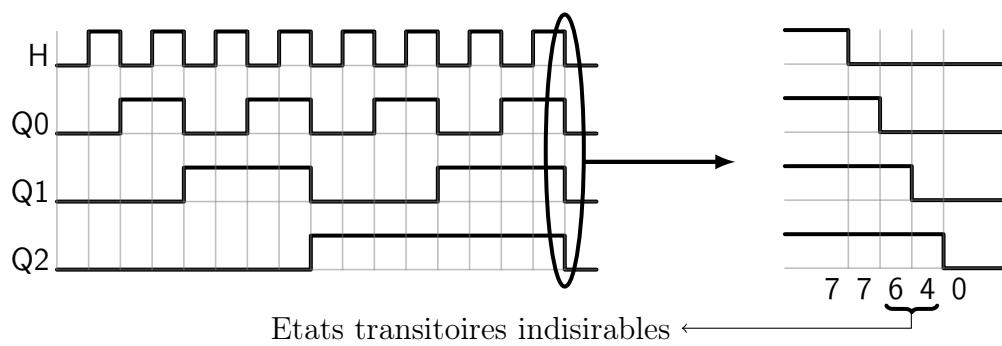

| 4.5.2.1.3 Inconvénients des compteurs asynchrones . .                     | 58        |

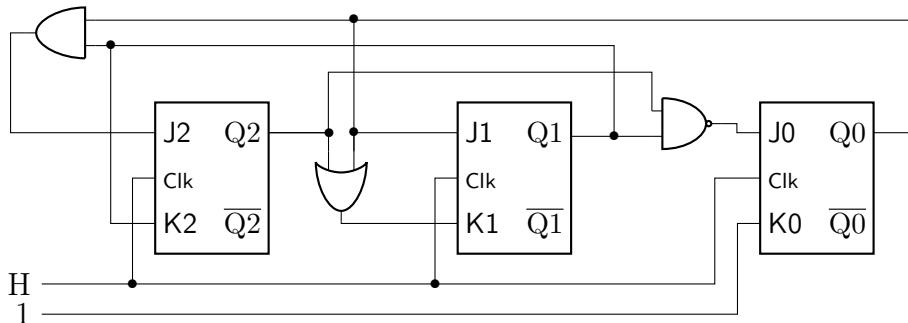

| 4.5.2.2 Les compteurs synchrones . . . . .                                | 59        |

| 4.5.3 Les mémoires à semi-conducteurs . . . . .                           | 60        |

| <b>5 Circuits intégrés</b>                                                | <b>63</b> |

| 5.1 Introduction . . . . .                                                | 63        |

| 5.2 Définition . . . . .                                                  | 63        |

| 5.3 Construction des circuits intégrés . . . . .                          | 64        |

| 5.4 Familles des circuits intégrés . . . . .                              | 66        |

| 5.4.1 Circuits intégrés TTL . . . . .                                     | 66        |

| 5.4.2 Circuits intégrés CMOS . . . . .                                    | 66        |

| 5.5 Circuits intégrés TTL des portes logiques de base . . . . .           | 67        |

| 5.6 Montage d'un circuit combinatoire via des circuits intégrés . . . . . | 68        |

# Chapitre 1

## Représentation des données

### 1.1 Introduction

Les données traitées par un ordinateur sont généralement de différents types. Elles peuvent être des textes, des nombres, des images, des vidéos, etc. Cependant, quel que soit leur type, ces données sont toujours stockées et manipulées par l'ordinateur sous forme binaire. Elles seront donc traitées comme une suite de 0 et de 1. Dans une telle représentation, l'unité d'information est le chiffre binaire (0 ou 1), que l'on appelle bit (pour binary digit, chiffre binaire).

Pour pouvoir traiter l'information dans l'ordinateur, il faut donc que cette dernière soit codée en binaire. Le codage d'une information consiste à établir une correspondance entre la représentation externe de cette information (le mot *Bien* ou le nombre 317 par exemple), et sa représentation interne dans l'ordinateur, qui est une suite de 0 et de 1.

On utilise la représentation binaire car elle est simple, facile à réaliser techniquement à l'aide de bistables (système à deux états réalisés à l'aide de transistors, voir le chapitre 4). Enfin, les opérations arithmétiques de base (addition, multiplication, etc.) sont faciles à exprimer en base 2 (noter que la table de multiplication se résume à  $0 \times 0 = 0$ ,  $1 \times 0 = 0$  et  $1 \times 1 = 1$ ).

### 1.2 Changements de bases

Dans cette première partie de ce chapitre et avant d'aborder la représentation des différents types de données, nous devons tout d'abord nous familiariser avec la représentation d'un nombre dans une base  $b$  quelconque.

Dans nos calculs quotidiens, on utilise le système décimal (base 10) pour représenter les nombres, c'est-à-dire que l'on écrit à l'aide de 10 chiffres distincts. Ce sont les chiffres de 0 à 9.

Ainsi, en base  $b$ , on utilise  $b$  chiffres distincts. Ce sont les chiffres de 0 à  $b - 1$ . Notons  $a_i$  la suite des chiffres utilisés pour écrire un nombre, chacun de ces chiffres est placé dans une position dans ce nombre. C'est ce que l'on appelle la notation positionnelle.

#### – Cas des nombres entiers

$$x = a_n a_{n-1} \dots + a_1 a_0 = \sum a_i \times b^i$$

$a_0$  est le chiffre de poids faible, et  $a_n$  le chiffre de poids fort.

**Exemples :**  $(1996)_{10} = 1 \times 10^3 + 9 \times 10^2 + 9 \times 10^1 + 6 \times 10^0$

$(101)_2 = 1 \times 2^2 + 0 \times 2^1 + 1 \times 2^0 = 4 + 0 + 1 = (5)_{10}$

La notation  $()_b$  indique que le nombre est écrit en base  $b$ .

- **Cas des nombres fractionnaires** (Les nombres fractionnaires sont ceux qui comportent des chiffres après la virgule).

$$x = a_n \dots a_1 a_0, a_{-1} \dots a_{-p} = a_n \times b^n + \dots + a_0 \times b^0 + a_{-1} \times b^{-1} + \dots + a_{-p} \times b^{-p}$$

$$\text{Exemple : } (12,346)_{10} = 1 \times 10^1 + 2 \times 10^0 + 3 \times 10^{-1} + 4 \times 10^{-2} + 6 \times 10^{-3}$$

**Remarques :**

1. En décimal,  $b = 10$ ,  $a_i \in \{0, 1, 2, 3, 4, 5, 6, 7, 8, 9\}$  ;

2. En binaire,  $b = 2$ ,  $a_i \in \{0, 1\}$  ; 2 chiffres binaires, ou bits ;

3. En hexadécimal,  $b = 16$ ,  $a_i \in \{0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, F\}$  (on utilise les 6 premières lettres de l'alphabet comme des chiffres).

### 1.2.1 Conversion du décimal en une base $b$ quelconque

- **Cas des nombres entiers :**

Dans le cas des nombres entiers (les nombres qui ne comportent pas de chiffres après la virgule), la conversion s'effectue par des divisions entières successives par la base  $b$ . On divise le nombre par la base, puis le quotient obtenu par la base, et ainsi de suite jusqu'à ce que l'on obtienne un quotient nul. Le nombre en base  $b$  résultant est obtenu en lisant les restes du dernier vers le premier.

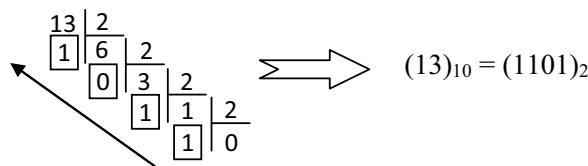

**Exemple :** Conversion du nombre décimal 13 en binaire ( $b = 2$ ) :

- **Cas des nombres fractionnaires :**

Dans le cas des nombres fractionnaires (les nombres qui comportent des chiffres après la virgule, notés :  $a_n a_{n-1} \dots a_1 a_0, a_{-1} a_{-2} \dots a_{-p}$ ), la partie entière est convertie par des divisions entières successives par  $b$  comme pour un nombre entier, alors que la partie fractionnaire est convertie par une multiplication successive par la base en répétant l'opération sur la partie fractionnaire du produit jusqu'à ce qu'elle soit nulle (ou que la précision voulue soit atteinte).

**Exemple :** Conversion du nombre décimal 13,125 en binaire ( $b = 2$ ) :

- **Partie entière :**  $(13)_{10} = (1101)_2$  par des divisions entières successives.

- **Partie fractionnaire :**

$$\begin{array}{rcl}

0,125 \times 2 = & \boxed{0},25 & \Rightarrow a_{-1} = \boxed{0} \quad \text{Poids binaire} \quad 0 \times 2^{-1} \\

0,25 \times 2 = & \boxed{0},50 & \Rightarrow a_{-2} = \boxed{0} \quad \text{Poids binaire} \quad 0 \times 2^{-2} \\

0,5 \times 2 = & \boxed{1},00 & \Rightarrow a_{-3} = \boxed{1} \quad \text{Poids binaire} \quad 1 \times 2^{-3}

\end{array}$$

Condition d'arrêt (partie fractionnaire du résultat égale à 0).

Donc,  $(13,125)_{10} = (1101,001)_2$

### 1.2.2 Conversion d'une base $b$ quelconque en décimal

La conversion se fait simplement en additionnant les produits des chiffres du nombre à convertir par les puissances de la base  $b$  correspondantes.

$$(a_n \dots a_0, a_{-1} \dots a_{-p})_b = (a_n \times b^n + \dots + a_0 \times b^0 + a_{-1} \times b^{-1} + \dots + a_{-p} \times b^{-p})_{10}$$

**Exemples :**

$$(10101, 01)_2 = 1 \times 2^4 + 0 \times 2^3 + 1 \times 2^2 + 0 \times 2^1 + 1 \times 2^0 + 0 \times 2^{-1} + 1 \times 2^{-2} = (21, 25)_{10}$$

$$(35, 4)_8 = 3 \times 8^1 + 5 \times 8^0 + 4 \times 8^{-1} = (29, 5)_{10}$$

$$(2F, 8)_{16} = 2 \times 16^1 + 15 \times 16^0 + 8 \times 16^{-1} = (47, 5)_{10}$$

### 1.2.3 Conversion d'une base $b = 2^n$ quelconque en binaire

La conversion consiste tout simplement à remplacer chaque chiffre par son équivalent binaire sur  $n$  bits.

**Exemples :**

$$(17, 5)_8 = \underbrace{001}_1, \underbrace{111}_7, \underbrace{101}_5 = (1111, 101)_2,$$

$$(17, 5)_{16} = \underbrace{0001}_1, \underbrace{0111}_7, \underbrace{0101}_5 = (10111, 0101)_2$$

### 1.2.4 Conversion du binaire en une base $b = 2^n$ quelconque

La conversion consiste à découper la séquence des chiffres binaires en un ensemble de groupes de  $n$  bits chacun. Le découpage doit commencer de la virgule vers la droite et vers la gauche. Si le nombre de bits de la partie entière (partie gauche) n'est pas un multiple de  $n$ , on doit compléter par des zéros à gauche de la séquence. De même, si le nombre de bits de la partie fractionnaire (partie droite) n'est pas un multiple de  $n$ , on doit compléter par des zéros à droite de la séquence. Après avoir découpé la séquence des chiffres binaire en groupes de  $n$  bits, on remplace chaque groupe par le chiffre de la base  $b$  correspondant.

**Exemples :**

$$(11011, 01)_2 = \underbrace{011}_3, \underbrace{011}_3, \underbrace{010}_2 = (33, 2)_8,$$

$$(11011, 01)_2 = \underbrace{0001}_1, \underbrace{1011}_B, \underbrace{0100}_4 = (1B, 4)_{16}$$

### 1.2.5 Conversion d'une base $b1$ en une base $b2$ ( $b1 \neq b2 \neq 10$ )

Pour réaliser une telle conversion, on doit passer par la base décimale comme base intermédiaire. C'est à dire, on doit d'abord convertir le nombre de la base  $b1$  en décimal avant de convertir, ensuite, le nombre décimal résultant en base  $b2$ .

**Exemple :**  $(25, 3)_6 = (?)_8 \Rightarrow (25, 3)_6 = (?)_{10} = (?)_8$

$$(25, 3)_6 = 2 \times 6^1 + 5 \times 6^0 + 3 \times 6^{-1} = (17, 5)_{10},$$

$$(17, 5)_{10} = \boxed{2} \times 8^1 + \boxed{1} \times 8^0 + \boxed{4} \times 8^{-1} = (21, 4)_8,$$

Donc,  $(25, 3)_6 = (21, 4)_8$

- **Cas particulier :** Lorsque  $b_1 = 2^n$  et  $b_2 = 2^m$  ( $n \neq m$ )

Dans le cas où  $b_1$  et  $b_2$  sont toutes les deux des puissances de 2, il est plus facile de passer par le binaire comme base intermédiaire que de passer par le décimal.

**Exemple :**  $(65, 7)_8 = (?)_{16} \Rightarrow (65, 7)_8 = (?)_2 = (?)_{16}$

$$(65, 7)_8 = \underbrace{110}_6, \underbrace{101}_5, \underbrace{111}_7 = (110101, 111)_2$$

$$(110101, 111)_2 = \underbrace{0011}_3, \underbrace{0101}_5, \underbrace{1110}_E = (35, E)_{16}$$

Donc,  $(65, 7)_8 = (35, E)_{16}$

## 1.3 Opérations arithmétiques en base $b$ quelconque

Les opérations arithmétiques de base, telles que l'addition, la soustraction, la multiplication et la division dans une base  $b$  quelconque sont effectuées de la même façon qu'en décimal.

### 1.3.1 Addition

L'addition en base  $b$  se fait généralement en suivant les mêmes règles qu'en décimal. C'est à dire, on commence à additionner les chiffres de poids faibles (les chiffres de droite) jusqu'au chiffre de poids le plus fort (celui tout à gauche). Lorsque la somme de deux chiffres de poids égaux dépasse la valeur de la base, on divise la somme par la base et on reporte le quotient aux chiffres du poids suivant (à gauche) et on inscrit le reste comme somme des deux chiffres du poids en cours.

**Exemple :**  $(15, 4)_6 + (12, 5)_6 = (?)_6 \Rightarrow \begin{array}{r} & 1 & 1 & 5, & 4 \\ & + & 1 & 2, & 5 \\ \hline & 3 & 2, & 3 \end{array}_6$

### 1.3.2 Soustraction

Pour la soustraction en base  $b$ , on procède comme en décimal. Quand la quantité à soustraire est supérieure à la quantité dont on soustrait, on emprunte 1 au voisin de gauche. Ce 1 emprunté ajoute la valeur de la base  $b$  à la quantité dont on soustrait afin de pouvoir réaliser la soustraction en cours. Ensuite, on retranche cet emprunt du bit de gauche et on fait la même chose pour les bits qui restent.

**Exemple 1 :**

$$(20)_3 - (2)_3 \Rightarrow \left( \begin{array}{r} 2 & 10 \\ - & 10 & 2 \\ \hline 1 & 1 \end{array} \right)_3$$

Dans cet exemple, on doit soustraire  $0 - 2$  pour les deux bits de poids faible, ce qui n'est pas possible car 0 est inférieur à 2. On emprunte donc 1 au bit de gauche ce qui va donner  $(3+0) - 2 = 1$ . Ensuite, on retranche cet emprunt du bit de gauche et on aura donc  $2 - 0 - 1 = 1$ .

**Exemple 2 :**  $(1010)_2 - (0111)_2 = (?)_2$

$$\left( \begin{array}{r} 1 & 0 & 1 & 10 & 0 \\ - & 0 & 1 & 1 & 1 \\ \hline 1 \end{array} \right)_2 \Rightarrow \left( \begin{array}{r} 1 & 0 & 11 & 1 & 10 & 0 \\ - & 0 & 1 & 1 & 1 & 1 \\ \hline 1 & 1 \end{array} \right)_2 \Rightarrow \left( \begin{array}{r} 1 & 10 & 0 & 11 & 1 & 10 & 0 \\ - & 1 & 0 & 1 & 1 & 1 & 1 \\ \hline 0 & 1 & 1 \end{array} \right)_2 \Rightarrow \left( \begin{array}{r} 1 & 10 & 0 & 11 & 1 & 10 & 0 \\ - & 1 & 0 & 1 & 1 & 1 & 1 \\ \hline 0 & 0 & 1 & 1 \end{array} \right)_2$$

### 1.3.3 Multiplication

La multiplication en base  $b$  est effectuée de la même façon qu'en décimal, en formant un produit partiel pour chaque chiffre du multiplicateur (sauf que la table du produit change d'une base à une autre). Pour finir, on additionne les résultats des différents produits partiels.

**Exemples :**

$$(15,4)_6 \times (2,5)_6 \Rightarrow \left( \begin{array}{r} \begin{array}{r} & 1 & 1 & 0 & 1 \\ \times & & 1 & 3 & 5 \\ & 2 & 5 \end{array} \\ \hline \begin{array}{r} 1 & 1 & 1 & 3 & 4 & 2 \\ 3 & 5 & 2 \\ \hline 5 & 3, & 0 & 2 \end{array} \end{array} \right)_6 ; \quad (1101)_2 \times (101)_2 \Rightarrow \left( \begin{array}{r} \begin{array}{r} & 1 & 1 & 0 & 1 \\ \times & & 1 & 0 & 1 \\ \hline & 1 & 1 & 1 & 0 & 1 \\ & 1 & 0 & 0 & 0 & 0 \\ \hline 1 & 1 & 1 & 0 & 1 \\ \hline 1 & 0 & 0 & 0 & 0 & 1 \end{array} \end{array} \right)_2$$

### 1.3.4 Division

La division en base  $b$  s'effectue comme en décimal à l'aide de soustractions et de décalages, sauf que la table de division change d'une base à une autre ce qui rend l'opération un peu compliquée. Cependant, cette opération est plus facile à effectuer en binaire. On prend le nombre de chiffres nécessaires pour la première division, puis on pose un 1 en quotient et on fait la soustraction, par la suite on abaisse un chiffre et on pose un 1 en quotient si l'on peut soustraire le diviseur, ou un 0 sinon et on recommence la même opération tant qu'il y a des chiffres qui ne sont pas encore abaissés.

**Exemple 1 :**

$$\left( \begin{array}{r} 1 & 0 & 1 & 1 & 0 \\ - 1 & 0 \\ \hline 0 & 0 \end{array} \middle| \begin{array}{r} 1 & 0 \\ 1 & 0 & 1 \end{array} \right)_2 \Rightarrow \left( \begin{array}{r} 1 & 0 & 1 & 1 & 0 \\ - 1 & 0 \\ \hline 0 & 0 & 1 & 1 \\ - 1 & 0 \\ \hline 0 & 1 \end{array} \middle| \begin{array}{r} 1 & 0 & 1 \\ 1 & 0 & 1 & 1 \end{array} \right)_2 \Rightarrow \left( \begin{array}{r} 1 & 0 & 1 & 1 & 0 \\ - 1 & 0 \\ \hline 0 & 0 & 1 & 1 \\ - 1 & 0 \\ \hline 0 & 1 & 0 \\ - 1 & 0 \\ \hline 0 & 0 \end{array} \middle| \begin{array}{r} 1 & 0 \\ 1 & 0 & 1 & 1 \end{array} \right)_2$$

**Exemple 2 :**

$$(1133,12)_4 \div (1,3)_4 \Rightarrow \left( \begin{array}{r} 1 & 1 & 3 & 3 & 1, & 2 \\ - 1 & 1 & 1 \\ \hline 0 & 0 & 2 & 3 \\ - 1 & 3 \\ \hline 1 & 1 & 0 & 1 & 1 \\ - 1 & 1 & 3 & 2 \\ \hline 0 & 0 & 3 & 2 \\ - 3 & 2 \\ \hline 0 & 0 \end{array} \middle| \begin{array}{r} 1 & 3 \\ 3 & 1 & 2, & 2 \end{array} \right)_4 \quad \begin{array}{l} (0)_4 \times (13)_4 = (0)_4 \\ (1)_4 \times (13)_4 = (13)_4 \\ (2)_4 \times (13)_4 = (32)_4 \\ (3)_4 \times (13)_4 = (111)_4 \end{array}$$

## 1.4 Représentation des données

Comme indiqué plus haut, les informations traitées par un ordinateur peuvent être de différents types (texte, nombres, images, vidéos, etc.) mais elles sont toujours représentées et manipulées par l'ordinateur sous forme binaire. Dans cette partie, on va se focaliser sur la représentation interne, dans la machine, des données numériques (celles qui peuvent être l'objet d'une opération arithmétique) et des données non numériques (par exemple, les symboles et les caractères constituant un texte). Les données traitées dans cette partie du chapitre ainsi que leur classification sont résumées par le graphe suivant :

## 1.4.1 Représentation des nombres entiers

### 1.4.1.1 Entiers naturels

Dans un ordinateur, les données sont codées sur un nombre de bits bien fixé,  $n$  bits par exemple. On rencontre habituellement des codages sur 8, 16, 32 ou 64 bits. Ainsi, les nombres entiers naturels sont représentés à l'intérieur de l'ordinateur par une simple conversion de ceux-ci en binaire de sorte que le résultat soit sur  $n$  bits, comme exigé par le système. Par conséquent, les résultats qui n'atteignent pas les  $n$  bits sont complétés à gauche par des zéros. Par ailleurs, si le nombre de bits du nombre converti dépasse les  $n$  bits exigés, celui-ci est considéré comme irreprésentable. En fait, un codage sur  $n$  bits ne permet de représenter que les nombres naturels compris entre 0 et  $2^{n-1}$ . Par exemple sur 1 octet, on pourra coder les nombres naturels de 0 à  $255 = 2^8 - 1$ .

**Exemple :**

Représentation du nombre naturel 21 sur 8 bits :  $(21)_{10} = (10101)_2 \Rightarrow (\underline{000}10101)_2$

Compléter par des zéros pour atteindre les 8 bits exigés

### 1.4.1.2 Entiers relatifs

Un entier relatif est un entier pouvant être positif ou négatif. Il possède en plus des chiffres qui le composent un autre symbole qui précise son signe. Il faut donc une méthode pour représenter ce type de nombres de sorte que l'on puisse les coder avec leur signe, tout en conservant les règles des opérations arithmétiques. Comme solution, plusieurs représentations ont été proposées, les plus connues sont : la représentation en signe avec valeur absolue (S+VA), la représentation en complément logique (complément restreint ou complément à 1) et la représentation en complément arithmétique (complément vrai ou complément à 2).

- 1. Représentation en signe et valeur absolue (S+VA) :** Dans cette méthode, on réserve le bit de poids fort (celui étant situé le plus à gauche) pour représenter le signe, les autres bits représentent la valeur absolue du nombre. On met le bit de poids fort à 0 pour repérer un nombre positif et on met ce même bit à 1 pour repérer un nombre négatif.

**Exemple :** Sur 8 bits :  $(00011011)_{S+VA}$  représente  $(+27)_{10}$

$(10011011)_{S+VA}$  représente  $(-27)_{10}$

## 2. Représentation en complément à 1 (complément logique ou restreint) :

Dans cette méthode, les entiers positifs ou nuls sont représentés comme pour les entiers naturels, sauf que le bit de poids fort est toujours à 0 : on n'utilise donc que  $n - 1$  bits pour représenter les valeurs de ces nombres. Alors que les entiers négatifs sont représentés en inversant les valeurs des  $n$  bits constituant la valeur binaire de leurs opposés (leurs équivalents en positif), c'est à dire chaque bit à 0 de ces derniers est remplacé par un 1 et vice-versa.

En d'autre terme, pour obtenir le codage en complément à 1 d'un nombre négatif, on code en binaire son équivalent positif (sa valeur absolue) sur  $n$  bits, puis on complémenté (ou inverse) tous les bits (c'est à dire, remplacer les 0 par des 1 et les 1 par des 0).

**Exemple :** Sur 8 bits :  $(00011011)_{C1}$  représente  $(+27)_{10}$

$(11100100)_{C1}$  représente  $(-27)_{10}$

## 3. Représentation en complément à 2 (complément arithmétique ou vrai) :

Dans cette méthode, les entiers positifs ou nuls sont toujours représentés comme pour les entiers naturels (le bit de poids fort est toujours à 0, comme en complément à 1) et les entiers négatifs sont représentés en ajoutant un 1 à leur représentation en complément à 1.

En d'autre terme, pour obtenir le codage en complément à 2 d'un nombre négatif, on code en binaire son équivalent positif (sa valeur absolue) sur  $n$  bits, puis on complémenté (ou inverse) tous les bits et on ajoute 1 au codage obtenu.

**Exemple :** Sur 8 bits :  $(00011011)_{C2}$  représente  $(+27)_{10}$

$(11100101)_{C2}$  représente  $(-27)_{10}$

### 1.4.2 Représentation des nombres réels

Deux méthodes principales sont utilisées pour représenter les nombres réels à l'intérieur d'un ordinateur : la représentation en virgule fixe et celle en virgule flottante.

#### 1.4.2.1 Représentation en virgule fixe

La représentation en virgule fixe est la méthode la plus simple et la plus utilisée sur les ordinateurs des premières générations. Le principe de cette représentation consiste, comme le montre la figure suivante, à réservé une partie de  $n$  bits pour représenter la partie entière du réel et une partie de  $m$  bits pour représenter la partie fractionnaire du réel, les deux parties sont précédées par un bit indiquant le signe du réel.

| Signe     | Partie entière | Partie fractionnaire |

|-----------|----------------|----------------------|

| ← 1 bit → | ← $n$ bits →   | ← $m$ bits →         |

**Exemple :**

Sur 16 bits :  $(1|0101011|10100000)_{VFixe}$  représente  $(-101011, 101)_2 = (-43, 625)_{10}$

En effet, la représentation en virgule fixe est une méthode très simple et permet d'effectuer les conversions très rapidement. Toutefois, cette structure de codage est trop rigide. Elle ne permet pas de représenter des nombres très grands, comme par exemple le nombre  $1,5 \times 10^{15}$ , ou ceux qui sont très proche de zéro, comme par exemple le

nombre  $1,5 \times 10^{-15}$ . Comme solution à ces problèmes, une autre méthode, à base de virgule flottante, a été introduite.

#### 1.4.2.2 Représentation en virgule flottante

La représentation des nombres réels à base de virgule flottante est la méthode la plus répandue dans la plupart des ordinateurs d'aujourd'hui, en particulier la représentation en virgule flottante avec la norme IEEE 754. Dans cette représentation, le nombre fractionnaire  $N$  est représenté sous la forme suivante :

| Signe (S) | Exposant décalé (ED)  | Mantisse (M)          |

|-----------|-----------------------|-----------------------|

| ← 1 bit → | ←———— $n$ bits —————→ | ←———— $m$ bits —————→ |

Les champs de cette représentation sont extraits de la notation dite scientifique du nombre à représenter, qui est donnée par la formule suivante :

$$N = (-1)^S \times 1, M \times 2^{E=ED-D}$$

L'exposant décalé ED est donc calculé par la formule :  $ED = E + D$ . Où  $E$  est l'exposant non décalé, alors que  $D$  est le décalage (biais) de l'exposant, c'est une valeur fixe donnée par la formule suivante (selon le format utilisé) :

$$D = 2^{\text{Taille de ED}-1} - 1$$

La taille des trois champs ( $S$ ,  $ED$  et  $M$ ) ainsi que la valeur de  $D$  sont liées de manière directe au format de représentation utilisé. Il y a trois formats pour la norme IEEE 754 :

- **Format simple précision (sur 32 bits)** : 1 bit pour le signe, 8 bits pour l'exposant décalé et 23 bits pour la mantisse. Dans ce format, la valeur de décalage  $D$  est égale à 127.

- **Format double précision (sur 64 bits)** : 1 bit pour le signe, 11 bits pour l'exposant décalé et 52 bits pour la mantisse. Dans ce format, la valeur de décalage  $D$  est égale à 1023.

- **Format précision étendue (sur 80 bits)** : 1 bit pour le signe, 15 bits pour l'exposant décalé et 64 bits pour la mantisse. Dans ce format, la valeur de décalage  $D$  est égale à 16383.

##### 1.4.2.2.1 Passage du décimal vers la représentation en virgule flottante

Pour représenter un nombre réel en virgule flottante selon la norme IEEE 754, on va suivre les étapes suivantes :

1. Convertir le nombre en binaire.

2. Normaliser le nombre en base 2, en l'écrivant sous la forme  $(-1)^S \times 1, M \times 2^E$ .

3. Calculer l'exposant décalé :  $ED = E + D$ , et convertir le résultat en binaire.

4. Remplir les trois champs de la représentation ( $S$ ,  $ED$  et  $M$ ).

**Exemple :**  $(-21,625)_{10} = (?)_{IEEE754(SP)}$

1.  $(-21,625)_{10} = (-10101, 101)_2$ .

2.  $(-10101, 101)_2 = (-1)^1 \times 1,0101101 \times 2^4.$

3.  $ED = E + D = 4 + 127 = (131)_{10} = (10000011)_2$

4.

|   |          |                                  |

|---|----------|----------------------------------|

| 1 | 10000011 | 01011010000000000000000000000000 |

|---|----------|----------------------------------|

Donc,  $(-21, 625)_{10} = (11000001101011010000000000000000)_{IEEE754(SP)}$

#### 1.4.2.2.2 Passage de la virgule flottante vers le décimal

Pour extraire la valeur décimale représentée par un code en virgule flottante selon la norme IEEE 754, on va suivre les étapes suivantes :

1. Extraire les trois champs de la représentation (S, ED et M).

2. Convertir l'exposant décalé en décimal, et calculer l'exposant non décalé :

$$E = ED - D.$$

3. Ecrire le nombre sous la forme  $(-1)^S \times 1, M \times 2^E.$  et dénormaliser le résultat.

4. Convertir le résultat en décimal.

**Exemple :**  $(11000001011011000000000000000000)_{IEEE754(SP)} = (?)_{10}$

1.

|   |          |                                  |

|---|----------|----------------------------------|

| 1 | 10000010 | 11011000000000000000000000000000 |

|---|----------|----------------------------------|

2.  $ED = (10000010)_2 = (130)_{10} \implies E = ED - D = 130 - 127 = (3)_{10}.$

3.  $N = (-1)^S \times 1, M \times 2^E = (-1)^1 \times 1, 11011 \times 2^3 = (-1110, 11)_2$

4.  $(-1110, 11)_2 = (-14, 75)_{10}$

Donc,  $(11000001011011000000000000000000)_{IEEE754(SP)} = (-14, 75)_{10}$

**Remarque :** Dans la norme IEEE 754, les exposants 00...0 et 11...1 sont interdits. Ils sont réservés pour représenter les cas particuliers suivants :

- La représentation :

|     |        |        |

|-----|--------|--------|

| $x$ | 00...0 | 00...0 |

|-----|--------|--------|

code la valeur zéro ( $x = 0$  ou 1).

- La représentation :

|   |        |        |

|---|--------|--------|

| 0 | 11...1 | 00...0 |

|---|--------|--------|

code la valeur plus infini ( $+\infty$ ).

- La représentation :

|   |        |        |

|---|--------|--------|

| 1 | 11...1 | 00...0 |

|---|--------|--------|

code la valeur moins infini ( $-\infty$ ).

- La représentation :

|     |        |                 |

|-----|--------|-----------------|

| $x$ | 00...0 | $M \neq 00...0$ |

|-----|--------|-----------------|

code un nombre dénormalisé (un nombre très proche de zéro).

- La représentation :

|     |        |                 |

|-----|--------|-----------------|

| $x$ | 11...1 | $M \neq 00...0$ |

|-----|--------|-----------------|

code un nombre indéterminé. On note cette configuration "NaN : Not a Number", et on l'utilise pour signaler des erreurs de calculs, comme par exemple une division par 0.

#### 1.4.3 Représentation des données non numériques (textes)

En plus des données numériques (entiers naturels, entiers relatifs et réels) abordées dans les sections précédentes de ce chapitre, les ordinateurs peuvent également traiter des données non numériques, telles que les données *alphanumériques* qui incluent des lettres alphabétiques majuscules et minuscules, des symboles de ponctuation (& @ , . ; # ", etc.), et des chiffres.

La représentation (codage) des données *alphanumériques* est souvent faite par une table de correspondance indiquant le code binaire représentant chaque caractère. Les deux codes les plus connus et les plus utilisés actuellement sont le code ASCII (American Standard Code for Information Interchange) et l'UNICODE (UNIversal CODE).

### 1.4.3.1 Code ASCII

Le code ASCII est la première norme adoptée par l'*American National Standards Institute* (ANSI) dans les années 1960 pour représenter les données alphanumériques. A cette époque, les ordinateurs fonctionnaient en 8 bits, ce qui était largement suffisant pour coder tous les caractères de l'anglais, majuscules et minuscules, les chiffres de 0 à 9 et certains caractères de contrôle (fin de ligne, tabulateur, etc) et de ponctuation (& @ , . ; # ", etc.).

| Parité  | Code du caractère |

|---------|-------------------|

| ←1 bit→ | 7 bits            |

Pour des raisons de fiabilité, les 8 bits du code ASCII sont divisés, comme le montre la figure ci-dessus, en deux parties. Les 7 premiers bits de poids faible représentent le code du caractère à représenter, alors que le 8ième bit (bit de poids fort), appelé bit de parité, est réservé pour contrôler et détecter les erreurs de transmission, car à l'époque les ordinateurs étaient liés à des télécopieurs qui servaient de point d'entrée des données, ce qui nécessitait un mécanisme de contrôle permettant de détecter les erreurs produites lors du transmission des données de ces derniers vers l'ordinateur. La valeur du bit de parité est donnée en fonction du nombre de bits à 1 dans le code du caractère à représenter. Si ce dernier est pair, le bit de parité va avoir la valeur 1, sinon il va prendre la valeur 0. La table suivante représente la codification ASCII en binaire, en hexadécimal et en décimal des différents caractères alphanumériques.

| Décimal | Hexa | Binaire | Caractère | Décimal | Hexa | Binaire | Caractère |

|---------|------|---------|-----------|---------|------|---------|-----------|

| 0       | 0    | 0000000 | NUL       | 32      | 20   | 0100000 | ESPACE    |

| 1       | 1    | 0000001 | SOH       | 33      | 21   | 0100001 | !         |

| 2       | 2    | 0000010 | STX       | 34      | 22   | 0100010 | "         |

| 3       | 3    | 0000011 | ETX       | 35      | 23   | 0100011 | #         |

| 4       | 4    | 0000100 | EOT       | 36      | 24   | 0100100 | \$        |

| 5       | 5    | 0000101 | ENQ       | 37      | 25   | 0100101 | %         |

| 6       | 6    | 0000110 | ACK       | 38      | 26   | 0100110 | &         |

| 7       | 7    | 0000111 | BEL       | 39      | 27   | 0100111 | ,         |

| 8       | 8    | 0001000 | BS        | 40      | 28   | 0101000 | (         |

| 9       | 9    | 0001001 | HT        | 41      | 29   | 0101001 | )         |

| 10      | A    | 0001010 | LF        | 42      | 2A   | 0101010 | *         |

| 11      | B    | 0001011 | VT        | 43      | 2B   | 0101011 | +         |

| 12      | C    | 0001100 | FF        | 44      | 2C   | 0101100 | ,         |

| 13      | D    | 0001101 | CR        | 45      | 2D   | 0101101 | -         |

| 14      | E    | 0001110 | SO        | 46      | 2E   | 0101110 | .         |

| 15      | F    | 0001111 | SI        | 47      | 2F   | 0101111 | /         |

| 16      | 10   | 0010000 | DLE       | 48      | 30   | 0110000 | 0         |

| 17      | 11   | 0010001 | DC1       | 49      | 31   | 0110001 | 1         |

| 18      | 12   | 0010010 | DC2       | 50      | 32   | 0110010 | 2         |

| 19      | 13   | 0010011 | DC3       | 51      | 33   | 0110011 | 3         |

| 20      | 14   | 0010100 | DC4       | 52      | 34   | 0110100 | 4         |

| 21      | 15   | 0010101 | NAK       | 53      | 35   | 0110101 | 5         |

| 22      | 16   | 0010110 | SYN       | 54      | 36   | 0110110 | 6         |

| 23      | 17   | 0010111 | ETB       | 55      | 37   | 0110111 | 7         |

| 24      | 18   | 0011000 | CAN       | 56      | 38   | 0111000 | 8         |

| 25      | 19   | 0011001 | EM        | 57      | 39   | 0111001 | 9         |

| 26      | 1A   | 0011010 | SUB       | 58      | 3A   | 0111010 | :         |

| 27      | 1B   | 0011011 | ESC       | 59      | 3B   | 0111011 | ;         |

| 28      | 1C   | 0011100 | FS        | 60      | 3C   | 0111100 | <         |

| 29      | 1D   | 0011101 | GS        | 61      | 3D   | 0111101 | =         |

| 30      | 1E   | 0011110 | RS        | 62      | 3E   | 0111110 | >         |

| 31      | 1F   | 0011111 | US        | 63      | 3F   | 0111111 | ?         |

| Décimal | Hexa | Binaire | Caractère | Décimal | Hexa | Binaire | Caractère |

|---------|------|---------|-----------|---------|------|---------|-----------|

| 64      | 40   | 1000000 | @         | 96      | 60   | 1100000 | '         |

| 65      | 41   | 1000001 | A         | 97      | 61   | 1100001 | a         |

| 66      | 42   | 1000010 | B         | 98      | 62   | 1100010 | b         |

| 67      | 43   | 1000011 | C         | 99      | 63   | 1100011 | c         |

| 68      | 44   | 1000100 | D         | 100     | 64   | 1100100 | d         |

| 69      | 45   | 1000101 | E         | 101     | 65   | 1100101 | e         |

| 70      | 46   | 1000110 | F         | 102     | 66   | 1100110 | f         |

| 71      | 47   | 1000111 | G         | 103     | 67   | 1100111 | g         |

| 72      | 48   | 1001000 | H         | 104     | 68   | 1101000 | h         |

| 73      | 49   | 1001001 | I         | 105     | 69   | 1101001 | i         |

| 74      | 4A   | 1001010 | J         | 106     | 6A   | 1101010 | j         |

| 75      | 4B   | 1001011 | K         | 107     | 6B   | 1101011 | k         |

| 76      | 4C   | 1001100 | L         | 108     | 6C   | 1101100 | l         |

| 77      | 4D   | 1001101 | M         | 109     | 6D   | 1101101 | m         |

| 78      | 4E   | 1001110 | N         | 110     | 6E   | 1101110 | n         |

| 79      | 4F   | 1001111 | O         | 111     | 6F   | 1101111 | o         |

| 80      | 50   | 1010000 | P         | 112     | 70   | 1110000 | p         |

| 81      | 51   | 1010001 | Q         | 113     | 71   | 1110001 | q         |

| 82      | 52   | 1010010 | R         | 114     | 72   | 1110010 | r         |

| 83      | 53   | 1010011 | S         | 115     | 73   | 1110011 | s         |

| 84      | 54   | 1010100 | T         | 116     | 74   | 1110100 | t         |

| 85      | 55   | 1010101 | U         | 117     | 75   | 1110101 | u         |

| 86      | 56   | 1010110 | V         | 118     | 76   | 1110110 | v         |

| 87      | 57   | 1010111 | W         | 119     | 77   | 1110111 | w         |

| 88      | 58   | 1011000 | X         | 120     | 78   | 1111000 | x         |

| 89      | 59   | 1011001 | Y         | 121     | 79   | 1111001 | y         |

| 90      | 5A   | 1011010 | Z         | 122     | 7A   | 1111010 | z         |

| 91      | 5B   | 1011011 | [         | 123     | 7B   | 1111011 |           |

| 92      | 5C   | 1011100 | \         | 124     | 7C   | 1111100 |           |

| 93      | 5D   | 1011101 | ]         | 125     | 7D   | 1111101 |           |

| 94      | 5E   | 1011110 | ^         | 126     | 7E   | 1111110 | ~         |

| 95      | 5F   | 1011111 | -         | 127     | 7F   | 1111111 |           |

Comme le montre la table des codes ASCII, les codes compris entre 0 et 31 ne représentent pas des caractères, ils ne sont pas affichables. Ces codes, souvent nommés *caractères de contrôles*, étaient utilisés pour contrôler la transmission des données du téléotype (point d'entrée) vers l'unité centrale (ordinateur). Ils indiquent des actions et des directives dont la signification de leurs codes est résumée dans la table suivante.

| Code | Signification                               | Code | Signification                              |

|------|---------------------------------------------|------|--------------------------------------------|

| NUL  | Absence de caractère                        | DLE  | Changement de signific (DataLink Escape)   |

| SOH  | Début d'entête (Start Of Heading)           | DC1  | Contrôle de périphérique 1 (Device Ctrl 1) |

| STX  | Début de texte (Start of Text)              | DC2  | Contrôle de périphérique 2 (Device Ctrl 2) |

| ETX  | Fin de texte (End of Text)                  | DC3  | Contrôle de périphérique 3 (Device Ctrl 3) |

| EOT  | Fin de transmission (End of Trans)          | DC4  | Contrôle de périphérique 4 (Device Ctrl 4) |

| ENQ  | Demande de réponse (Enquiry)                | NAK  | Accusé de reception négatif (Neg Ack)      |

| ACK  | Accusé de réception (Acknowledge)           | SYN  | Attente synchronisée (Synchronous idle)    |

| BEL  | Signal sonore ou 'bip' (Bell)               | ETB  | Fin transmission bloc (End Trans Block)    |

| BS   | Retour arrière (Backspace)                  | CAN  | Annuler transmission précédente (Cancel)   |

| HT   | Tabulation horizontale (Horizontal Tab)     | EM   | Fin de média (End of Medium)               |

| LF   | Saut de ligne (Line Feed)                   | SUB  | Remplacement (Substitute)                  |

| VT   | Tabulation verticale (Vertical Tab)         | ESC  | Contrôle d'extension (Escape)              |

| FF   | Saut de page (Form Feed)                    | FS   | Séparateur de fichier (File Separator)     |

| CR   | Retour chariot (Carriage Return)            | GS   | Séparateur de groupe (Group Separator)     |

| SO   | Sortir des caractères réguliers (Shift Out) | RS   | Séparateur d'enregistrement (Record Sep)   |

| SI   | Retour aux caractères réguliers (Shift In)  | US   | Séparateur d'unité (Unit Separator)        |

En code ASCII, les lettres se suivent dans l'ordre alphabétique (codes 65 à 90 pour les majuscules, 97 à 122 pour les minuscules), ce qui simplifie la comparaison entre les différents caractères. De plus, les codes des caractères majuscules et minuscules sont donnés de sorte que le passage du majuscule au minuscule, ou l'inverse, soit plus facile. Par exemple, pour passer du code d'un caractère majuscule à son code en minuscule, il suffit de modifier la valeur du 6<sup>ème</sup> bit du code à la valeur 1, ce qui revient à ajouter la valeur 32 à son code ASCII décimal.

#### 1.4.3.2 Code ASCII étendu

Afin de permettre l'utilisation des caractères accentués ainsi que d'autres caractères spéciaux, absents de la table ASCII basique, le huitième bit qui servait pour le contrôle de parité, contrôlé rendu de plus en plus inutile face aux améliorations de la fiabilité des transmissions, a été utilisé par la suite pour fournir un jeu de caractères "étendu" pour les valeurs entre 128 et 255. Cette extension a permis l'émergence de plusieurs normes différentes. On trouve par exemple la norme ISO Latin-1 ou ISO 8859-1 pour l'alphabet de l'europe occidentale, ISO Latin-2 ou ISO 8859-2 pour l'alphabet de l'europe centrale, ISO Latin-3 ou ISO 8859-3 pour l'alphabet de l'europe du sud (turc, maltais, etc), ISO Latin-4 ou ISO 8859-4 pour l'alphabet de l'europe du nord (estonien, letton, lituanien, groenlandais et sami), ISO Latin-5 ou ISO 8859-5 pour l'alphabet cyrillique comme le bulgare, le biélorusse, le russe et le macédonien, etc.

#### 1.4.3.3 Encodage UNICODE

En effet, le code ASCII étendu a conduit à l'apparition de plusieurs normes différentes, ce qui a rendu difficile le passage d'un document d'une plate-forme à une autre. Pour résoudre ce problème et afin de satisfaire à tous les besoins mondiaux, les organismes de normalisation ont proposé en 1991 l'encodage UNICODE (pour UNIversal CODE en anglais). Ce dernier code les caractères sur 16 bits, offrant donc 65 536 ( $2^{16}$ ) codes différents, ce qui permet d'incorporer presque tous les alphabets existants (arabe, arménien, latin de base, chinois, japonais, cyrillique, bengali, etc.) dans une seule table de codage. Il est compatible avec le code ASCII basique (les 128 premiers caractères Unicode sont les mêmes que ceux de la table ASCII basique) ainsi que le code ASCII étendu ISO-8859-1 (les 256 premiers caractères Unicode sont les mêmes que ceux de l'encodage ISO-8859-1). Par exemple le caractère A est codé (41)<sub>16</sub> en ASCII et (0041)<sub>16</sub> en Unicode. La table suivante montre les plages (en hexadécimal) de codes de quelques alphabets en Unicode.

| Alphabet      | Plage des codes   | Alphabet  | Plage des codes    |

|---------------|-------------------|-----------|--------------------|

| Latin         | [U+0000 à U+024F] | Hébreu    | [U+0590 à U+05FF]  |

| Grec et Copte | [U+0370 à U+03FF] | Arabe     | [U+0600 à U+06FF]  |

| Cyrillique    | [U+0400 à U+052F] | Maldivien | [U+0780 U+07BF]    |

| Arménien      | [U+0530 à U+058F] | Éthiopien | [ U+1200 à U+137F] |

En Unicode, un caractères prend 2 octets. Par conséquent, un texte en Unicode prendra deux fois plus de place qu'en ASCII. Ce qui représente un gaspillage, notamment pour les textes anglais et latins (français, espagnol, allemand, etc.). Car la grande majorité des caractères de ces langues utilisent seulement le code ASCII. Seuls quelques rares caractères nécessitent l'Unicode.

Pour résoudre ce problème, le format UTF-8 (Universal Transformation Format 8 bis) a été introduit. Un texte en UTF-8 est écrit en ASCII (sur 8 bits), et dès qu'on a besoin d'un caractère qui n'appartient pas au code ASCII, on utilise l'Unicode en précédant le code de ce dernier par un caractère spécial signalant que le caractère suivant est en Unicode.

#### 1.4.4 Autres codes particuliers

##### 1.4.4.1 Code BCD

Le code BCD (Binary Coded Decimal) est un code particulier qui permet de coder un nombre décimal en binaire. Dans ce code, chaque chiffre du nombre décimal est codé, comme le montre la table suivante, en binaire naturel sur 4 bits. Ainsi, pour un nombre décimal à  $n$  chiffres, on aura une représentation BCD de  $4 \times n$  chiffres binaires.

| Décimal | 0    | 1    | 2    | 3    | 4    | 5    | 6    | 7    | 8    | 9    |

|---------|------|------|------|------|------|------|------|------|------|------|

| BCD     | 0000 | 0001 | 0010 | 0011 | 0100 | 0101 | 0110 | 0111 | 1000 | 1001 |

**Exemples :**

$$\begin{aligned} (258)_{10} &= (0010\ 0101\ 1000)_{BCD} \\ (32)_{10} &= (0011\ 0010)_{BCD} \\ (69)_{10} &= (0110\ 1001)_{BCD} \\ (4096)_{10} &= (0100\ 0000\ 1010\ 0110)_{BCD} \end{aligned}$$

##### 1.4.4.1.1 Addition en BCD

Pour additionner deux nombres en BCD, il suffit de :

1. Procéder à l'addition en binaire naturel ;

2. Tester le résultat chiffre par chiffre, c'est à dire 4 bits par 4 bits, en commençant par les poids faibles et ajouter la valeur  $(6)_{10}$ , c'est à dire  $(0110)_2$ , à tout quartet incorrect dépassant la valeur  $(9)_{10}$  (c'est à dire supérieure à  $(1001)_2$ ) ou ayant une retenue sur l'opération de son dernier bit.

**Exemple :**

$$\left( \begin{array}{r} 69537 \\ + 18383 \\ \hline 87920 \end{array} \right)_{10} \Leftrightarrow \left( \begin{array}{r} 0110\ 1001\ 0101\ 0011\ 0111 \\ + 0001\ 1000\ 0011\ 1000\ 0011 \\ \hline 1000\ 0001\ 1000\ 1011\ 1010 \\ + 0110\ 0110\ 0110\ 0110\ 0110 \\ \hline 1000\ 0111\ 1001\ 0010\ 0000 \end{array} \right)_{BCD}$$

Quartets incorrects

Rajout de  $(0110)_2$

##### 1.4.4.1.2 Soustraction en BCD

Pour soustraire deux nombres en BCD, il suffit de :

1. Procéder à la soustraction en binaire naturel ;

2. Tester le résultat chiffre par chiffre, c'est à dire 4 bits par 4 bits, en commençant par les poids faibles et soustraire la valeur  $(6)_{10}$ , c'est à dire  $(0110)_2$ , de tout quartet incorrect dépassant la valeur  $(9)_{10}$  (c'est à dire supérieure à  $(1001)_2$ ) ou ayant emprunté un 1 pour son dernier bit.

**Exemple :**

$$\left( \begin{array}{r} 61537 \\ - 19383 \\ \hline 42154 \end{array} \right)_{10} \Leftrightarrow \left( \begin{array}{cccccc} 0110 & 0001 & 0101 & 0011 & 0111 \\ - 0001 & 1001 & 0011 & 1000 & 0011 \\ \hline 0100 & 1000 & 0001 & 1011 & 0100 \\ - & 0110 & 0110 & & \\ \hline 0100 & 0010 & 0001 & 0101 & 0100 \end{array} \right)_{BCD}$$

Quartets incorrects

Soustraire  $(0110)_2$

#### 1.4.4.2 Code Gray

Le code Gray, appelé aussi code binaire réfléchi, est un code adjacent dans lequel un seul bit change quand on passe d'un nombre entier au nombre entier suivant ou au nombre entier précédent (c'est à dire, d'un nombre  $n$  au nombre  $n + 1$  ou au nombre  $n - 1$ ). La table suivante montre le codage des chiffres décimaux en code gray.

| Décimal | 0    | 1    | 2    | 3    | 4    | 5    | 6    | 7    | 8    | 9    |

|---------|------|------|------|------|------|------|------|------|------|------|

| BCD     | 0000 | 0001 | 0011 | 0010 | 0110 | 0111 | 0101 | 0100 | 1100 | 1101 |

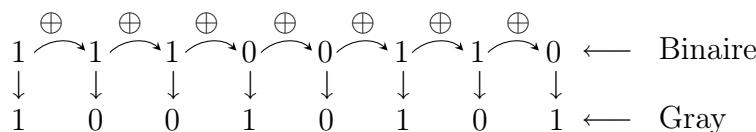

##### 1.4.4.2.1 Transcodage Binaire - Gray

Pour convertir un nombre  $b = b_n b_{n-1} \dots b_1 b_0$  du binaire naturel au binaire réfléchi ou gray  $g = g_n g_{n-1} \dots g_1 g_0$ , il suffit de changer le bit qui précède directement un bit 1 ou bien de calculer les valeurs  $g_i, 0 \leq i \leq n$  du code gray comme suit :

$$\begin{cases} g_n = b_n \\ g_i = b_i \oplus b_{i+1} \quad 0 \leq i \leq n-1 \end{cases}$$

**Exemple :**  $(11100110)_2 = (10010101)_{gray}$

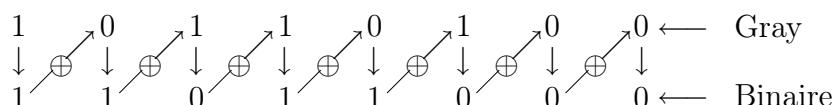

##### 1.4.4.2.2 Transcodage Gray - Binaire

Pour convertir un nombre  $g = g_n g_{n-1} \dots g_1 g_0$  du binaire réfléchi ou gray au binaire naturel  $b = b_n b_{n-1} \dots b_1 b_0$ , il suffit de calculer les valeurs  $b_i, 0 \leq i \leq n$  du code binaire naturel comme suit :

$$\begin{cases} b_n = g_n \\ b_i = b_{i+1} \oplus g_i \quad 0 \leq i \leq n-1 \end{cases}$$

**Exemple :**  $(10110100)_{gray} = (11011000)_2$

#### 1.4.4.3 Codes détecteurs d'erreur

Les données traitées par un ordinateur peuvent subir des modifications involontaires lors de leur transmission ou lors de leur stockage en mémoire. Donc, il est parfois important d'utiliser des codes permettant de détecter les erreurs dues à ces modifications. Dans cette optique, plusieurs variantes du code BCD ont été introduites. Parmi celles-ci, on trouve le code *2 dans 5*, le code *Johnson* et le code *biquinaire*. Dans le code *2 dans 5*, un chiffre décimal est codé sur 5 bits, avec 2 et seulement 2 bits ayant la valeur 1. Le code *Johnson* est un code BCD adjacent à 5 bits dont les 1 constituant le code sont toujours placés en un seul groupe qui se déplace d'un chiffre décimal au chiffre suivant. De son côté, le code *biquinaire* est une variante du code BCD où les chiffres décimaux sont codé sur 7 bits, avec toujours un et un seul bit à 1 dans les deux bits de gauche et un et un seul bits 1 dans les cinq bits de droite. La table suivante montre le codage des différents chiffres décimaux pour chacun de ces trois codes.

| Décimal    | 0       | 1       | 2       | 3       | 4       | 5       | 6       | 7       | 8       | 9       |

|------------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|

| 2 dans 5   | 00011   | 00101   | 00110   | 01001   | 01010   | 01100   | 10001   | 10010   | 10100   | 11000   |

| Johnson    | 00000   | 00001   | 00011   | 00111   | 01111   | 11111   | 11110   | 11100   | 11000   | 10000   |

| biquinaire | 0100001 | 0100010 | 0100100 | 0101000 | 0110000 | 1000001 | 1000010 | 1000100 | 1001000 | 1010000 |

**Exemples :**  $(2058)_{10} = (00110\ 00011\ 01100\ 10100)_2 \text{ dans } 5$

$= (00011\ 00000\ 11111\ 11000)_{\text{Johnson}}$

$= (0100100\ 0100001\ 1000001\ 1001000)_{\text{biquinaire}}$

# Chapitre 2

## Algèbre de Boole

### 2.1 Introduction

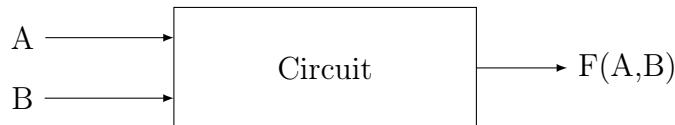

Les machines numériques sont constituées d'un ensemble de circuits électroniques. Chaque circuit fournit une fonction bien déterminée (addition, comparaison, etc.).

Pour concevoir et réaliser un circuit numérique, on doit avoir un modèle mathématique de la fonction réalisée par ce circuit. La réalisation de ce modèle est basé sur l'algèbre de Boole. Ainsi dans ce chapitre, et avant d'aborder la notion des circuits combinatoires et des circuits séquentiels qui seront détaillées dans les chapitres ultérieurs, nous devons tout d'abord se familiariser avec la notion de l'algèbre de boole.

### 2.2 Définition de l'algèbre de Boole

L'algèbre de Boole est une algèbre définie sur un ensemble comprenant deux éléments (vrai ou faux) que nous noterons 0 et 1 ( $\{0,1\}$ ). Les variables de cette algèbre sont appelées variables logiques et elles peuvent prendre l'une de ces deux valeurs. Il s'agit donc d'un outil mathématique qui permet d'établir la relation entre un ensemble de variables logiques via des fonctions appelées fonctions logiques. La sortie de celles-ci ne peut, elle aussi, prendre que deux valeurs (0 et 1).

Les opérateurs de base utilisés par une fonction logique pour relier ses variables d'entrée sont :

- La somme booléenne, appelé aussi le OU logique (notation  $+$ )

- Le produit booléen, appelé aussi le ET logique (notation  $\cdot$ )

- La négation (complément) booléenne, appelé aussi le NON logique (notation  $\neg$ )

Voici un exemple d'une fonction logique :

$$F(A, B, C) = \overline{A} \cdot \overline{B} \cdot C + (\overline{A} + B + C) \cdot (A + \overline{B})$$

En électronique, l'algèbre de Boole est définie comme étant l'outil mathématique qui permet d'établir la relation entre les entrées et les sorties du système à réaliser (synthèse du système). Réciproquement, cet outil est utilisé également pour déterminer les règles de fonctionnement d'un système logique existant (analyse du système).

## 2.3 Théorèmes fondamentaux de l'algèbre de Boole

Une algèbre de Boole doit vérifier les axiomes et les théorèmes suivants :

| axiome ou théorème | Opérateur OU (+)                    | Opérateur ET (·)                            |

|--------------------|-------------------------------------|---------------------------------------------|

| Commutativité      | $A+B = B+A$                         | $A \cdot B = B \cdot A$                     |

| Distributivité     | $A+(B \cdot C) = (A+B) \cdot (A+C)$ | $A \cdot (B+C) = (A \cdot B) + (A \cdot C)$ |

| Associativité      | $(A+B)+C = A+(B+C)$                 | $(A \cdot B) \cdot C = A \cdot (B \cdot C)$ |

| Idempotence        | $A+A = A$                           | $A \cdot A = A$                             |

| Complémentation    | $A+\bar{A} = 1$                     | $A \cdot \bar{A} = 0$                       |

| Involution         |                                     | $\bar{\bar{A}} = A$                         |

| Elément neutre     | $A+0 = A$                           | $A \cdot 1 = A$                             |

| Elément dominant   | $A+1 = 1$                           | $A \cdot 0 = 0$                             |

| Absorption         | $A+(A \cdot B) = A$                 | $A \cdot (A+B) = A$                         |

| Allégement         | $A+(\bar{A} \cdot B) = A+B$         | $A \cdot (\bar{A}+B) = A \cdot B$           |

| Inclusion          | $(A+B) \cdot (A+\bar{B}) = A$       | $(A \cdot B)+(A \cdot \bar{B}) = A$         |

| De Morgan          | $\bar{A+B} = \bar{A} \cdot \bar{B}$ | $\bar{A \cdot B} = \bar{A} + \bar{B}$       |

## 2.4 Fonctions de base de l'algèbre de Boole

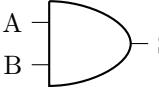

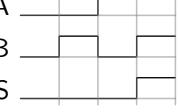

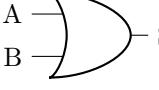

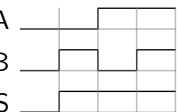

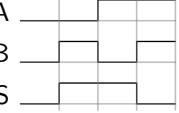

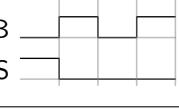

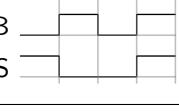

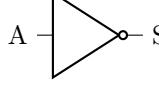

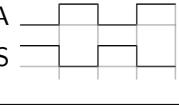

| Fonction                   | Symbol                                                                              | Equation                     | Table de vérité                                                                                                                                                                                                                          | Chronogramme |   |   |   |   |   |                                                                                       |   |   |   |   |   |   |   |   |                                                                                       |

|----------------------------|-------------------------------------------------------------------------------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---|---|---|---|---|---------------------------------------------------------------------------------------|---|---|---|---|---|---|---|---|---------------------------------------------------------------------------------------|

| ET<br>AND                  |  | $S = A \cdot B$              | <table border="1"> <tr> <th>A</th><th>B</th><th>S</th></tr> <tr> <td>0</td><td>0</td><td>0</td></tr> <tr> <td>0</td><td>1</td><td>0</td></tr> <tr> <td>1</td><td>0</td><td>0</td></tr> <tr> <td>1</td><td>1</td><td>1</td></tr> </table> | A            | B | S | 0 | 0 | 0 | 0                                                                                     | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 1 |  |

| A                          | B                                                                                   | S                            |                                                                                                                                                                                                                                          |              |   |   |   |   |   |                                                                                       |   |   |   |   |   |   |   |   |                                                                                       |

| 0                          | 0                                                                                   | 0                            |                                                                                                                                                                                                                                          |              |   |   |   |   |   |                                                                                       |   |   |   |   |   |   |   |   |                                                                                       |

| 0                          | 1                                                                                   | 0                            |                                                                                                                                                                                                                                          |              |   |   |   |   |   |                                                                                       |   |   |   |   |   |   |   |   |                                                                                       |

| 1                          | 0                                                                                   | 0                            |                                                                                                                                                                                                                                          |              |   |   |   |   |   |                                                                                       |   |   |   |   |   |   |   |   |                                                                                       |

| 1                          | 1                                                                                   | 1                            |                                                                                                                                                                                                                                          |              |   |   |   |   |   |                                                                                       |   |   |   |   |   |   |   |   |                                                                                       |

| OU<br>OR                   |  | $S = A + B$                  | <table border="1"> <tr> <th>A</th><th>B</th><th>S</th></tr> <tr> <td>0</td><td>0</td><td>0</td></tr> <tr> <td>0</td><td>1</td><td>1</td></tr> <tr> <td>1</td><td>0</td><td>1</td></tr> <tr> <td>1</td><td>1</td><td>1</td></tr> </table> | A            | B | S | 0 | 0 | 0 | 0                                                                                     | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 |  |

| A                          | B                                                                                   | S                            |                                                                                                                                                                                                                                          |              |   |   |   |   |   |                                                                                       |   |   |   |   |   |   |   |   |                                                                                       |

| 0                          | 0                                                                                   | 0                            |                                                                                                                                                                                                                                          |              |   |   |   |   |   |                                                                                       |   |   |   |   |   |   |   |   |                                                                                       |

| 0                          | 1                                                                                   | 1                            |                                                                                                                                                                                                                                          |              |   |   |   |   |   |                                                                                       |   |   |   |   |   |   |   |   |                                                                                       |

| 1                          | 0                                                                                   | 1                            |                                                                                                                                                                                                                                          |              |   |   |   |   |   |                                                                                       |   |   |   |   |   |   |   |   |                                                                                       |

| 1                          | 1                                                                                   | 1                            |                                                                                                                                                                                                                                          |              |   |   |   |   |   |                                                                                       |   |   |   |   |   |   |   |   |                                                                                       |

| OU<br>Exclusif<br>XOR      |  | $S = A \oplus B$             | <table border="1"> <tr> <th>A</th><th>B</th><th>S</th></tr> <tr> <td>0</td><td>0</td><td>0</td></tr> <tr> <td>0</td><td>1</td><td>1</td></tr> <tr> <td>1</td><td>0</td><td>1</td></tr> <tr> <td>1</td><td>1</td><td>0</td></tr> </table> | A            | B | S | 0 | 0 | 0 | 0                                                                                     | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 0 |  |

| A                          | B                                                                                   | S                            |                                                                                                                                                                                                                                          |              |   |   |   |   |   |                                                                                       |   |   |   |   |   |   |   |   |                                                                                       |

| 0                          | 0                                                                                   | 0                            |                                                                                                                                                                                                                                          |              |   |   |   |   |   |                                                                                       |   |   |   |   |   |   |   |   |                                                                                       |

| 0                          | 1                                                                                   | 1                            |                                                                                                                                                                                                                                          |              |   |   |   |   |   |                                                                                       |   |   |   |   |   |   |   |   |                                                                                       |

| 1                          | 0                                                                                   | 1                            |                                                                                                                                                                                                                                          |              |   |   |   |   |   |                                                                                       |   |   |   |   |   |   |   |   |                                                                                       |

| 1                          | 1                                                                                   | 0                            |                                                                                                                                                                                                                                          |              |   |   |   |   |   |                                                                                       |   |   |   |   |   |   |   |   |                                                                                       |

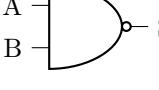

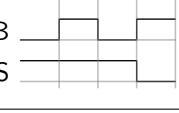

| NON-ET<br>NAND             |  | $S = \bar{A} \cdot \bar{B}$  | <table border="1"> <tr> <th>A</th><th>B</th><th>S</th></tr> <tr> <td>0</td><td>0</td><td>1</td></tr> <tr> <td>0</td><td>1</td><td>1</td></tr> <tr> <td>1</td><td>0</td><td>1</td></tr> <tr> <td>1</td><td>1</td><td>0</td></tr> </table> | A            | B | S | 0 | 0 | 1 | 0                                                                                     | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 0 |  |

| A                          | B                                                                                   | S                            |                                                                                                                                                                                                                                          |              |   |   |   |   |   |                                                                                       |   |   |   |   |   |   |   |   |                                                                                       |

| 0                          | 0                                                                                   | 1                            |                                                                                                                                                                                                                                          |              |   |   |   |   |   |                                                                                       |   |   |   |   |   |   |   |   |                                                                                       |

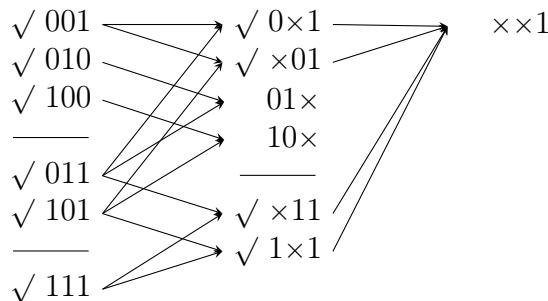

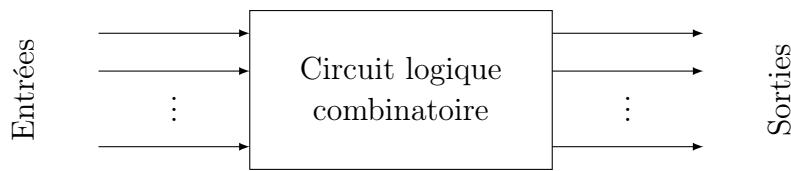

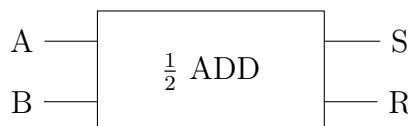

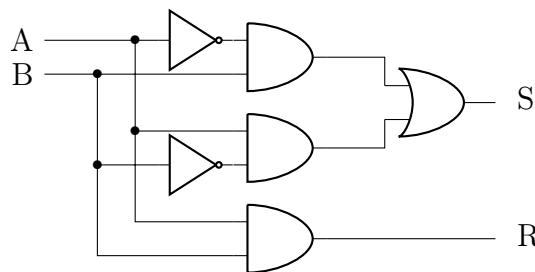

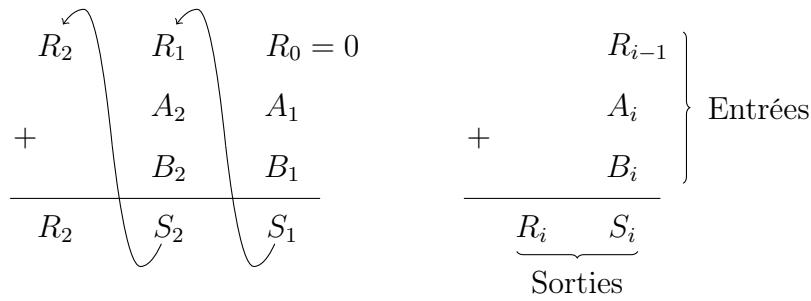

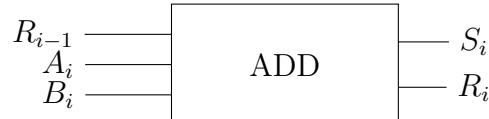

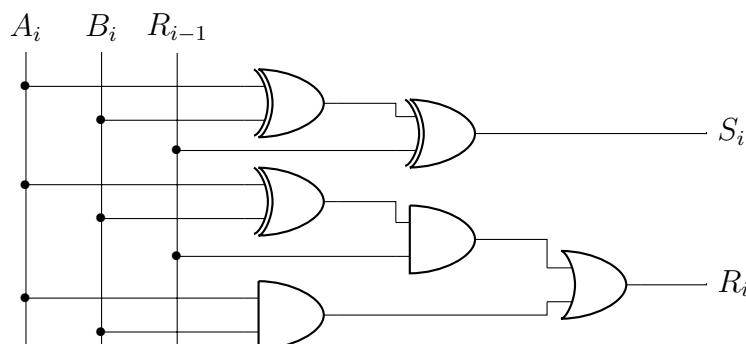

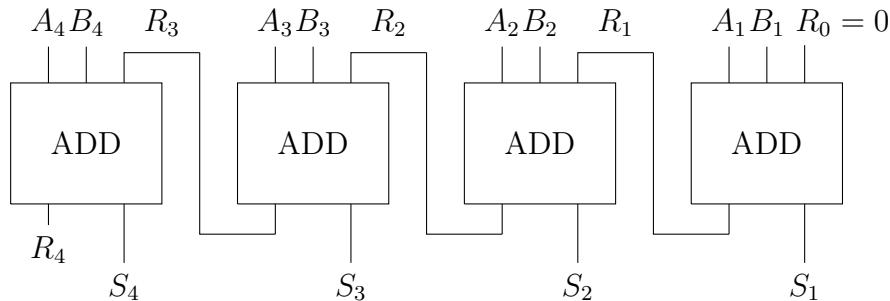

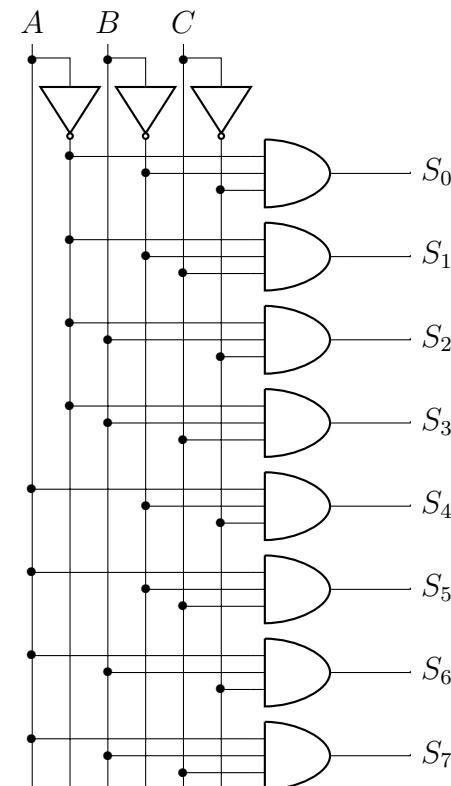

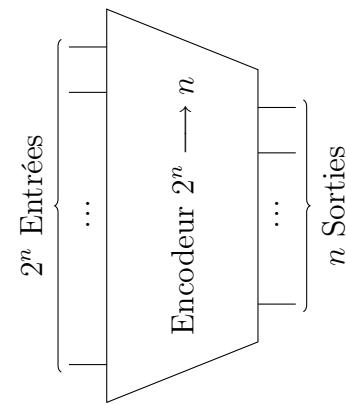

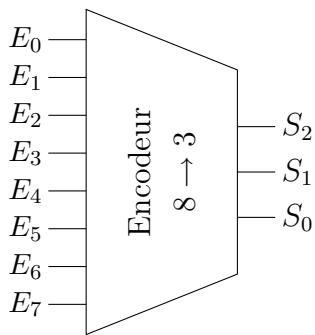

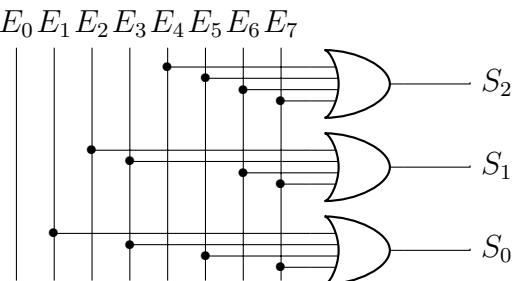

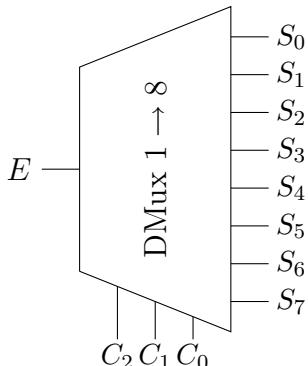

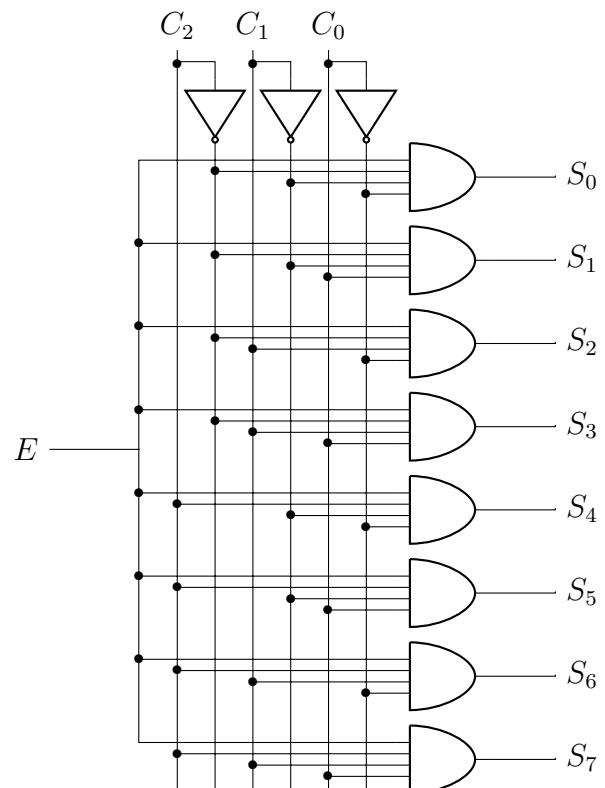

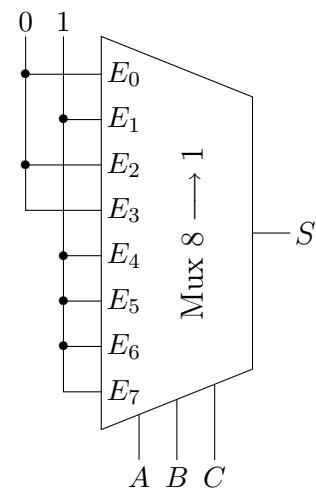

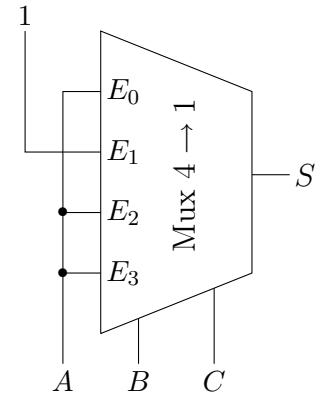

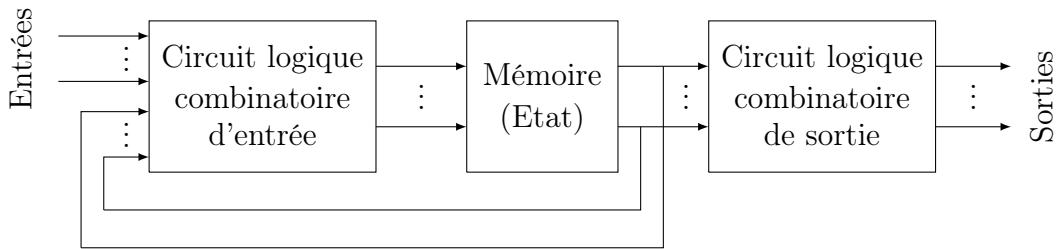

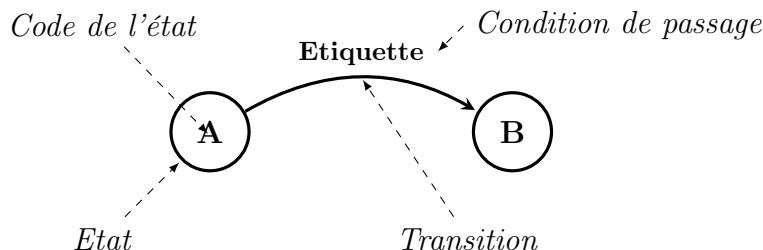

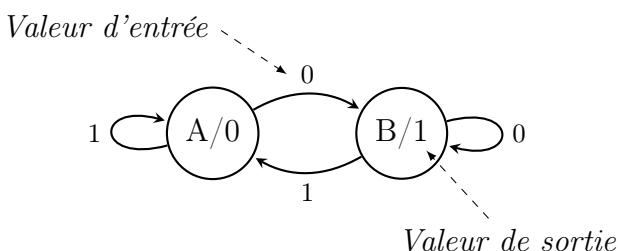

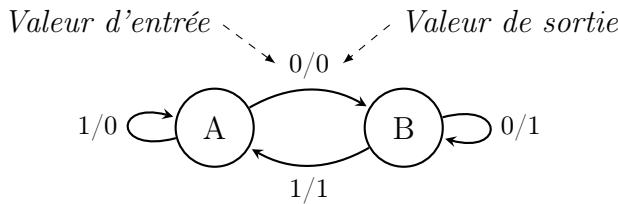

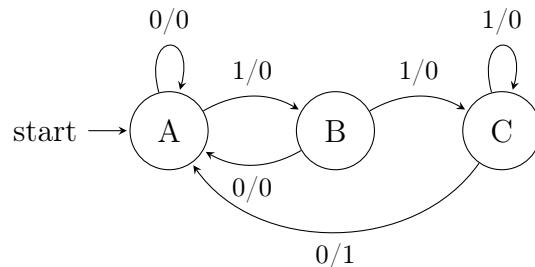

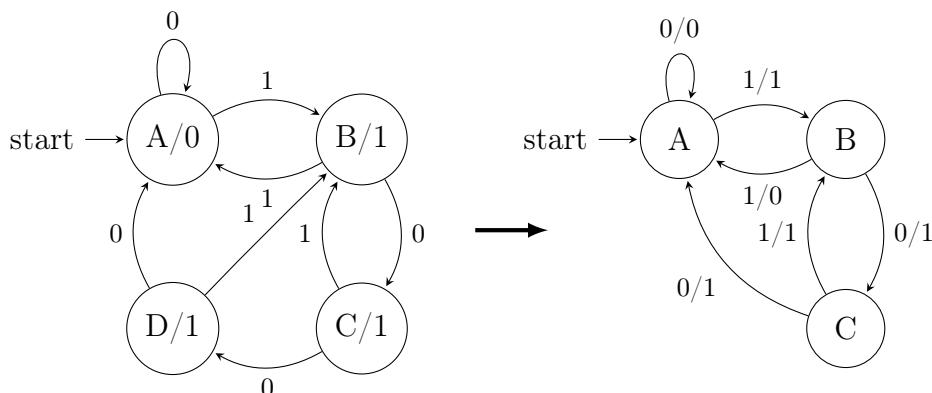

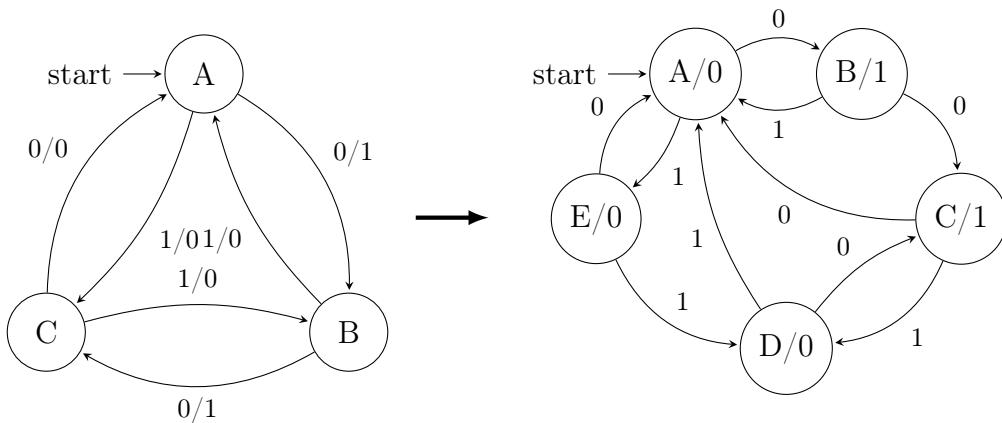

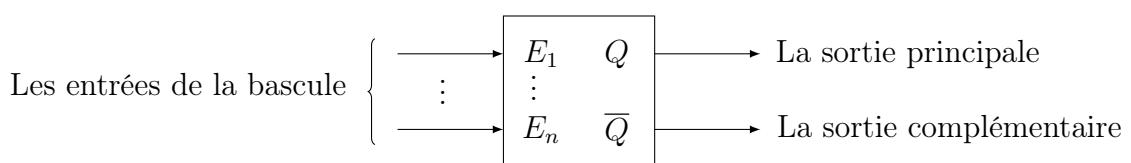

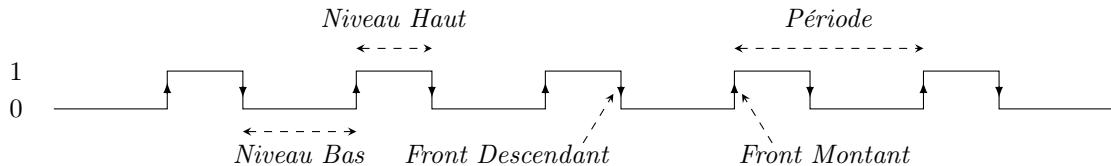

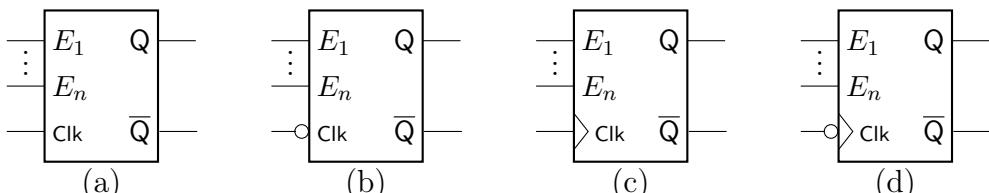

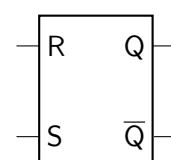

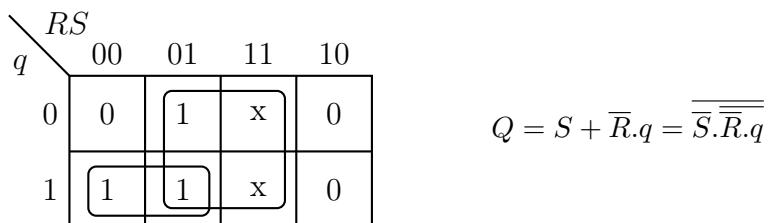

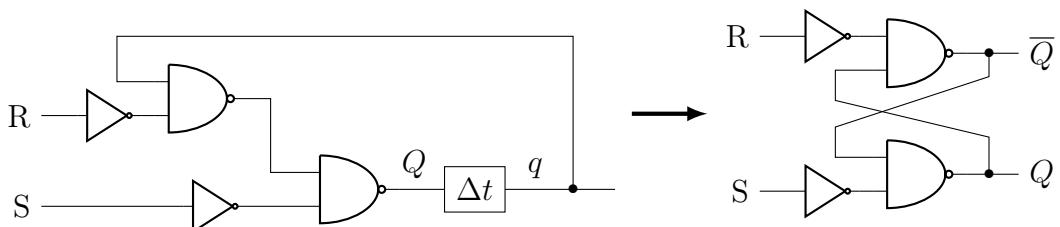

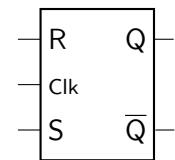

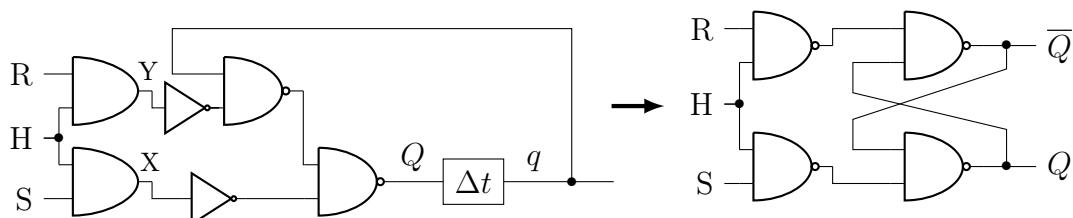

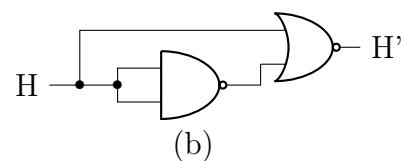

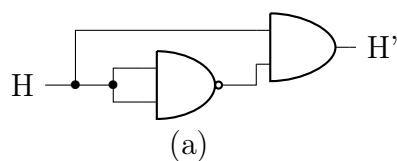

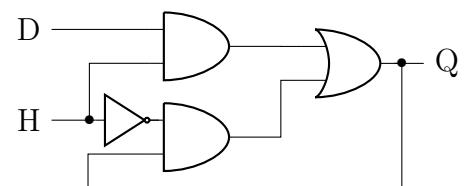

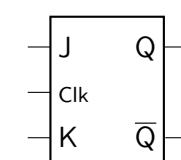

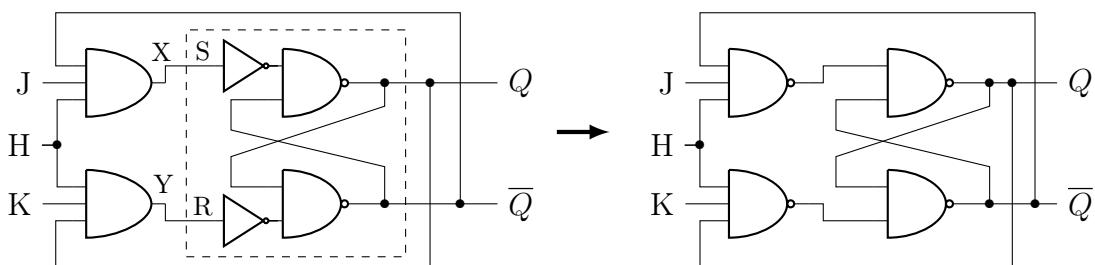

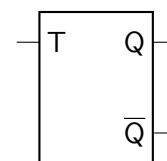

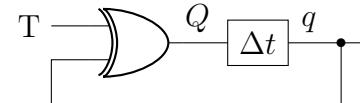

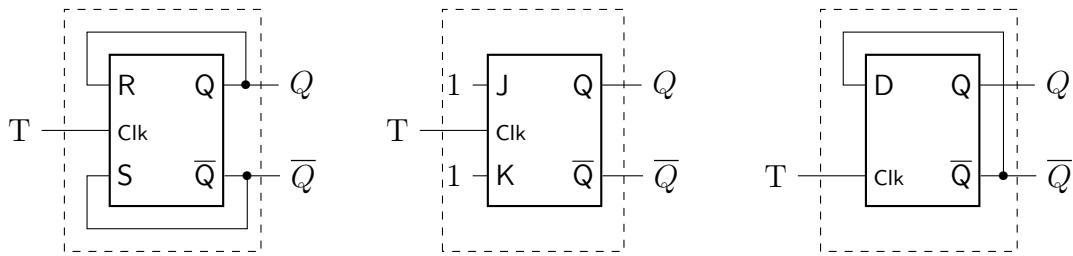

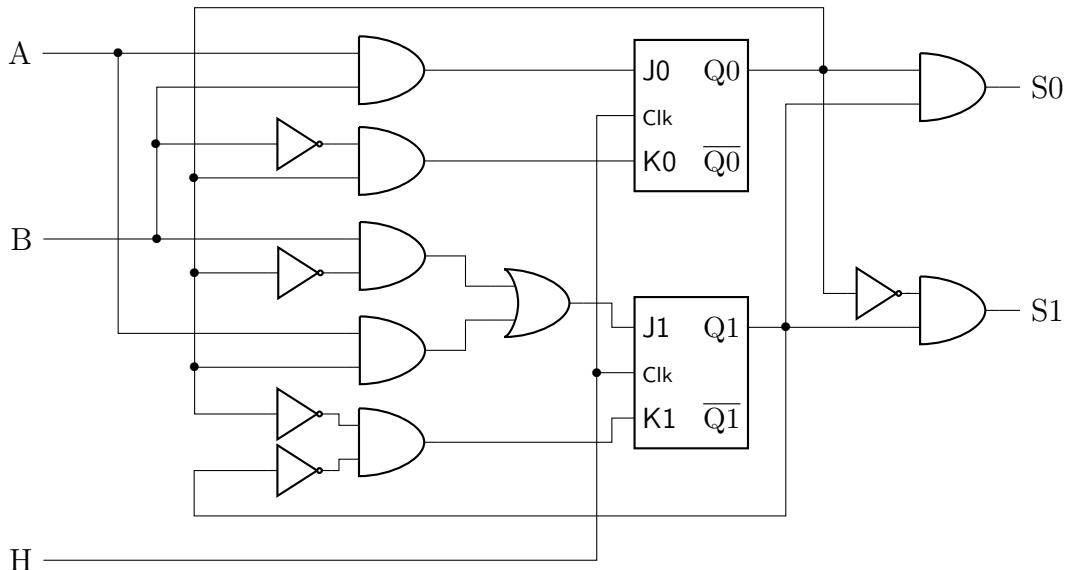

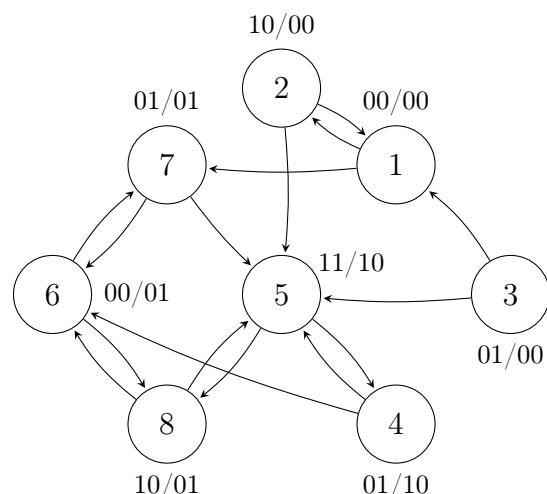

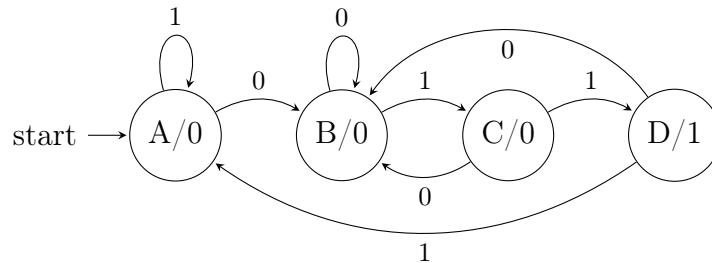

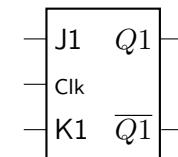

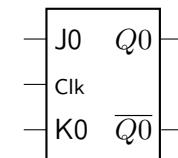

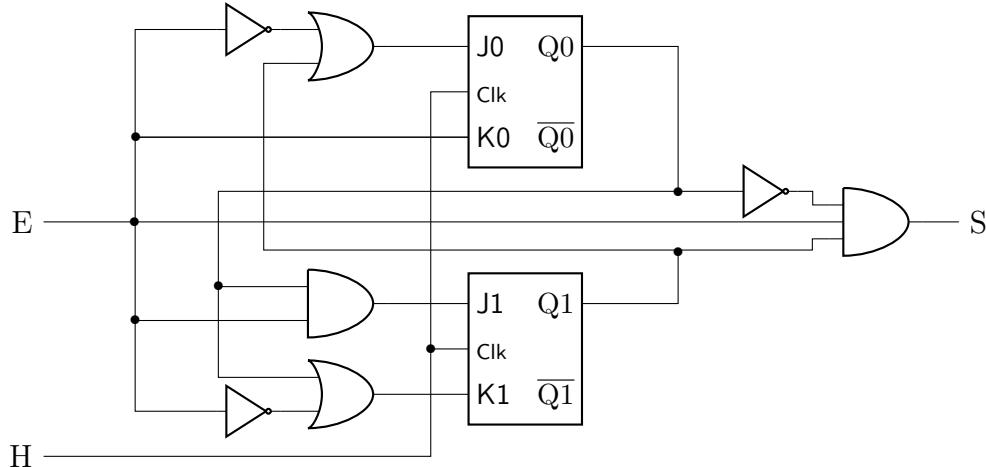

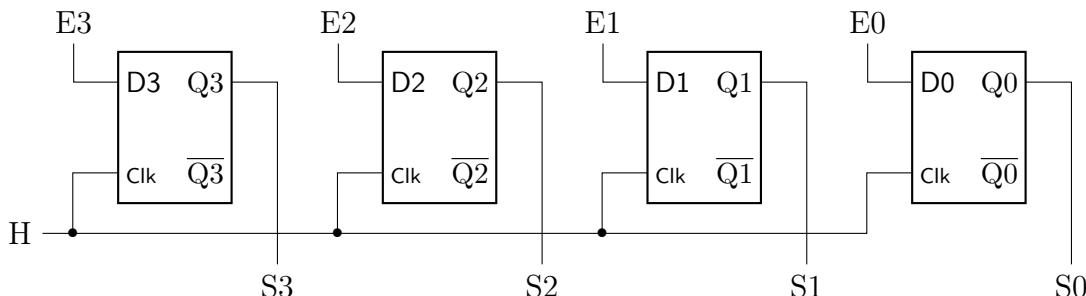

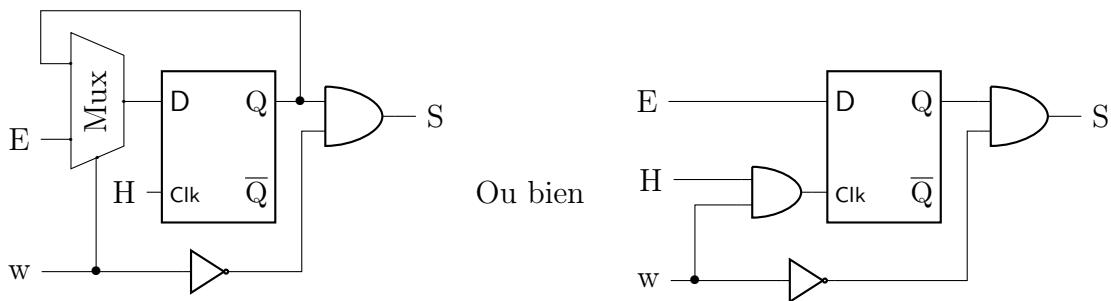

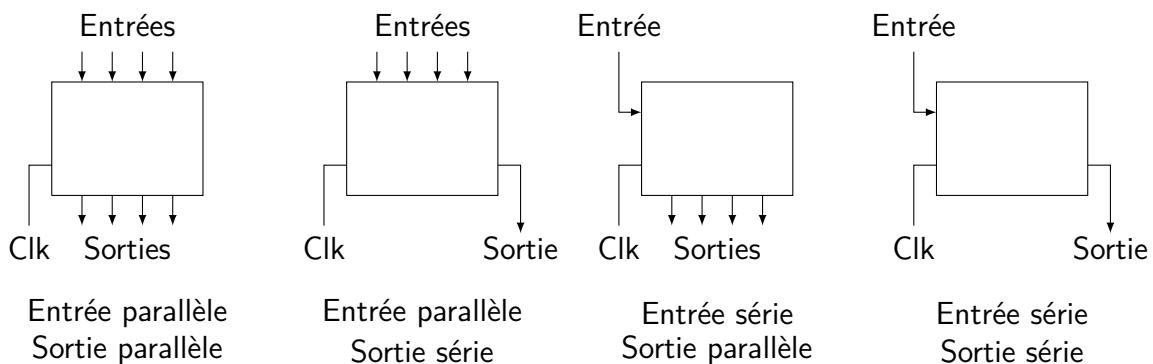

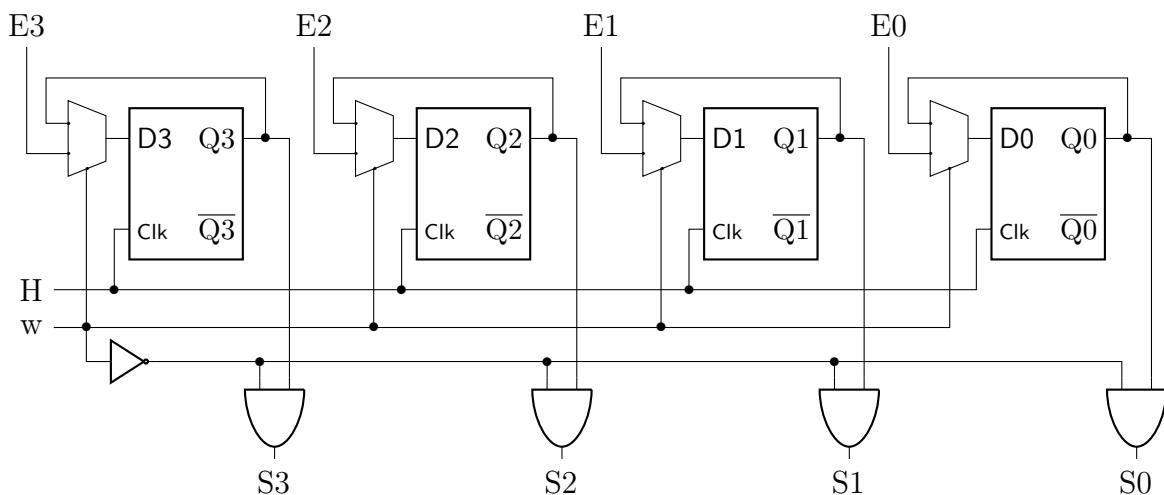

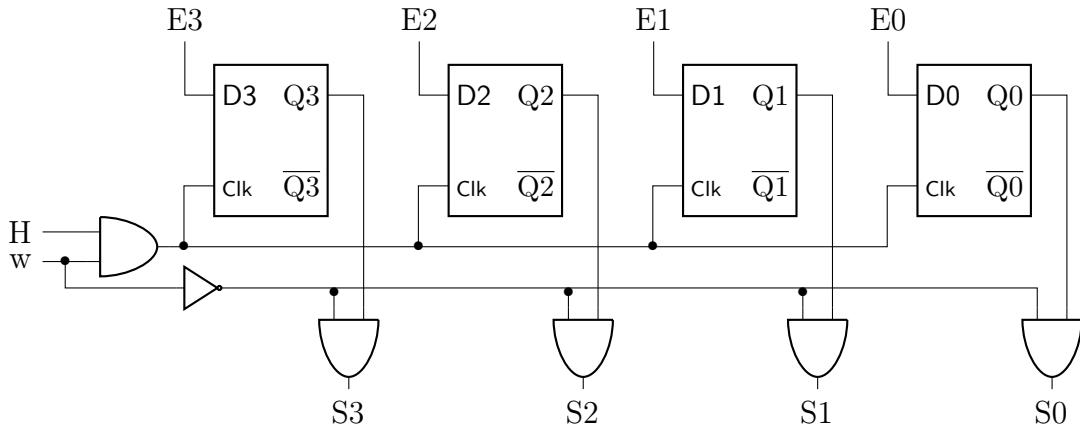

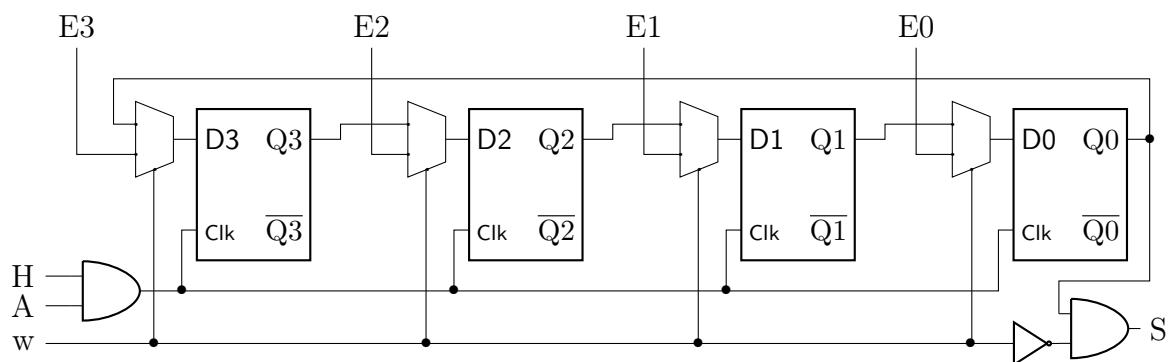

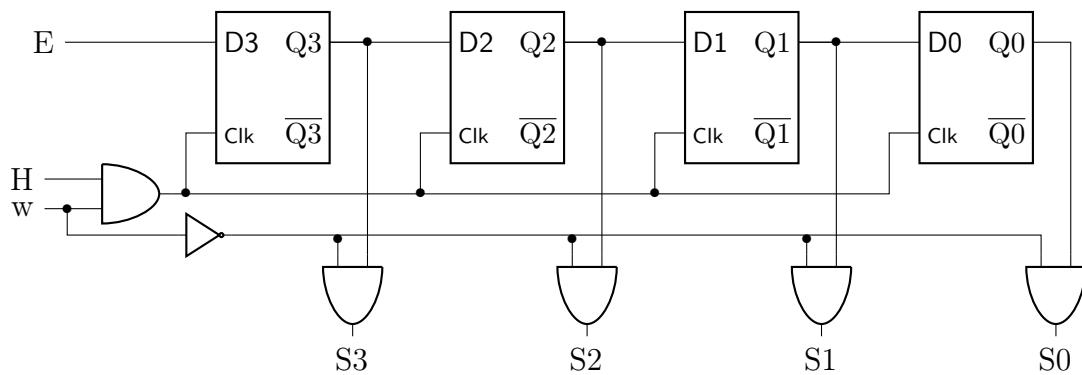

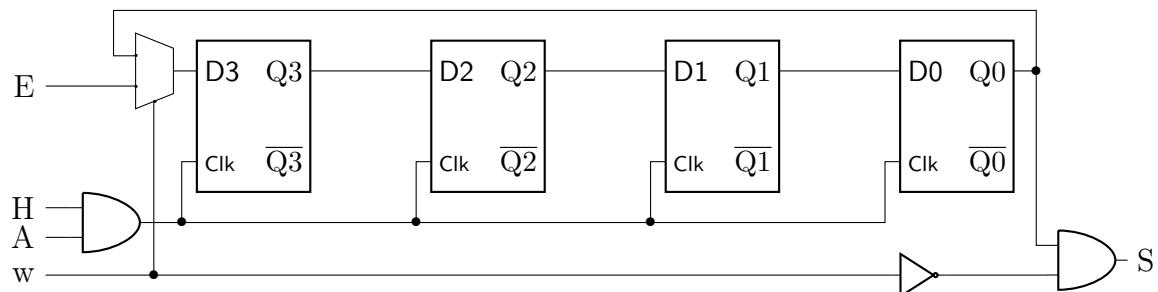

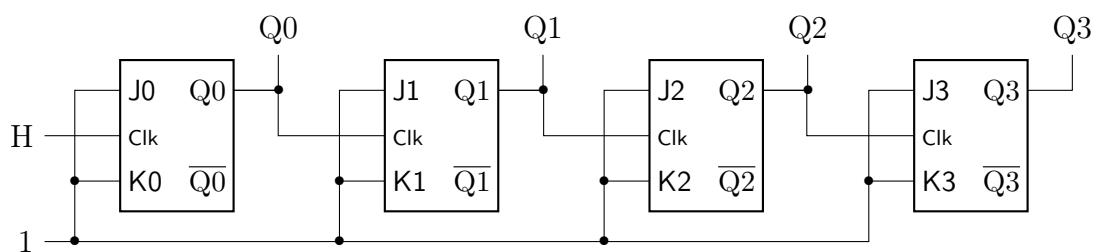

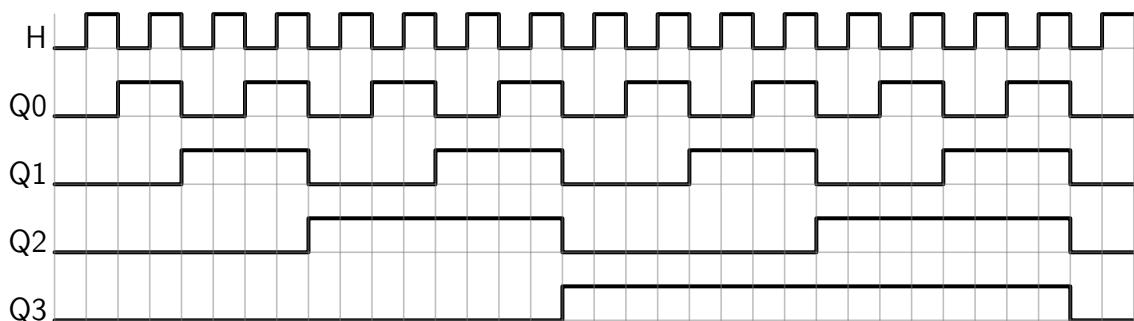

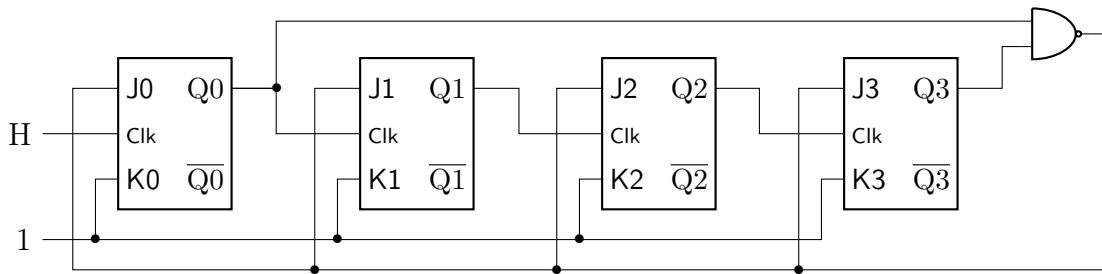

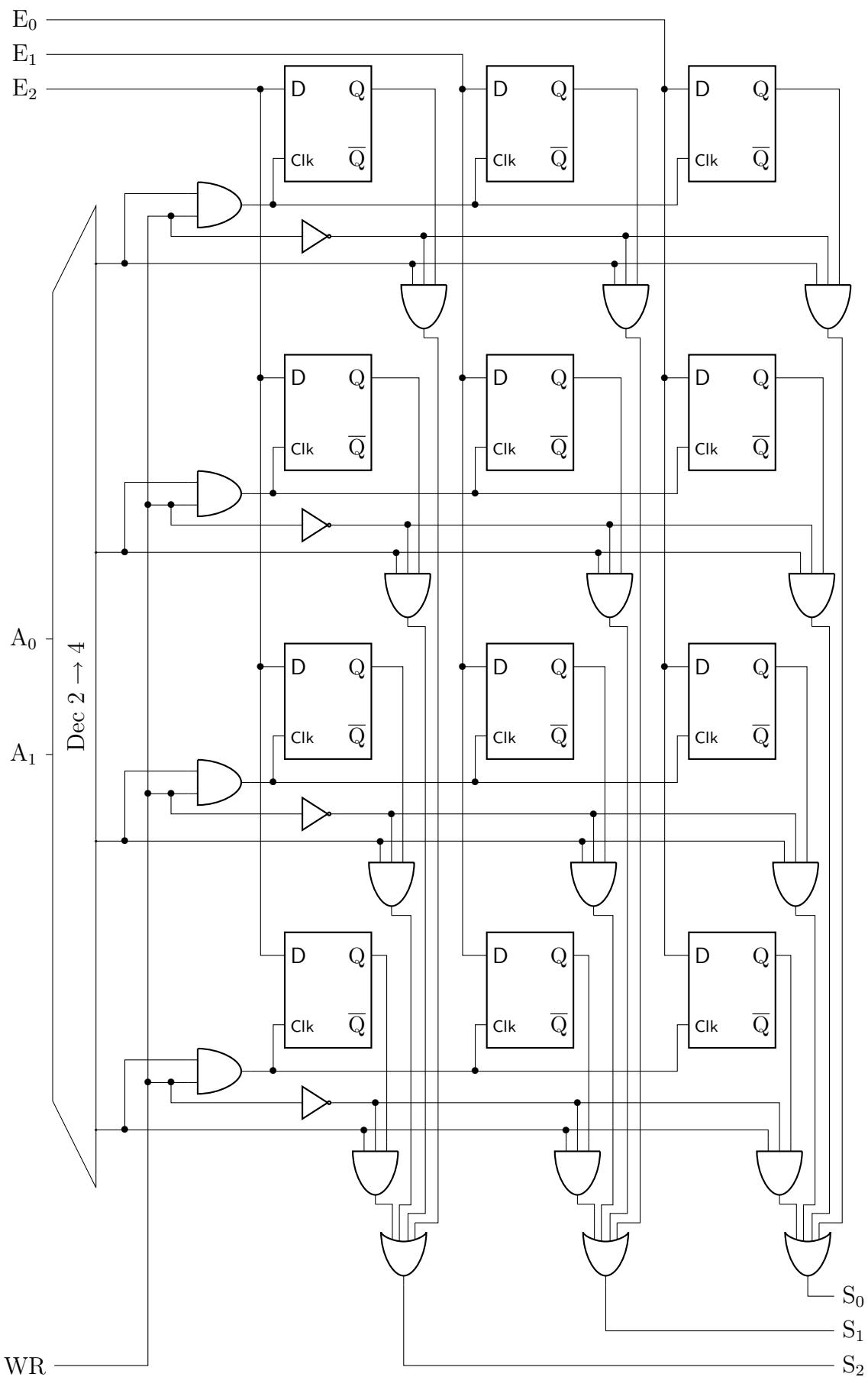

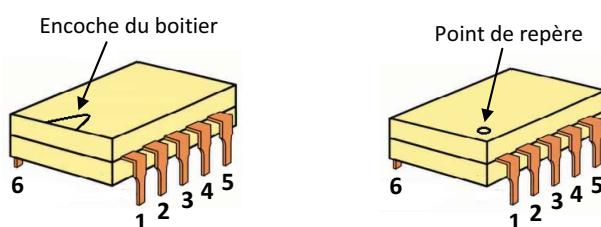

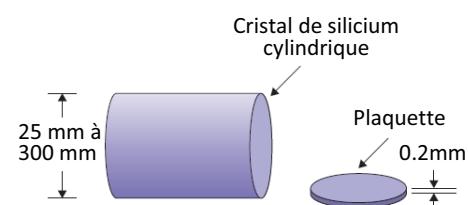

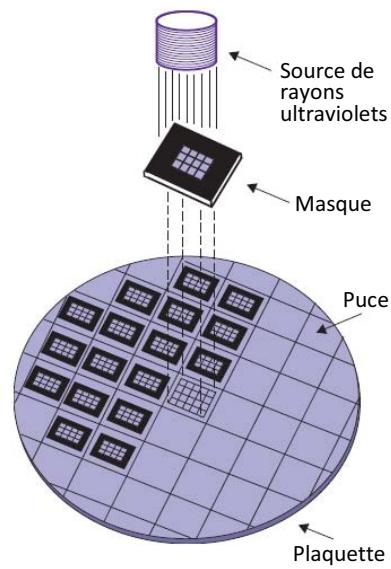

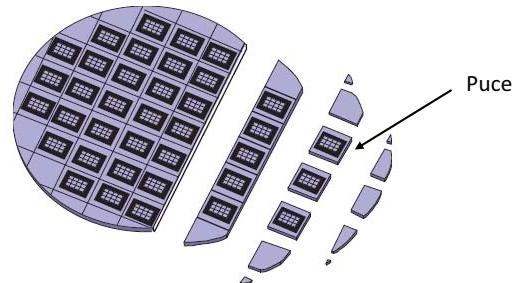

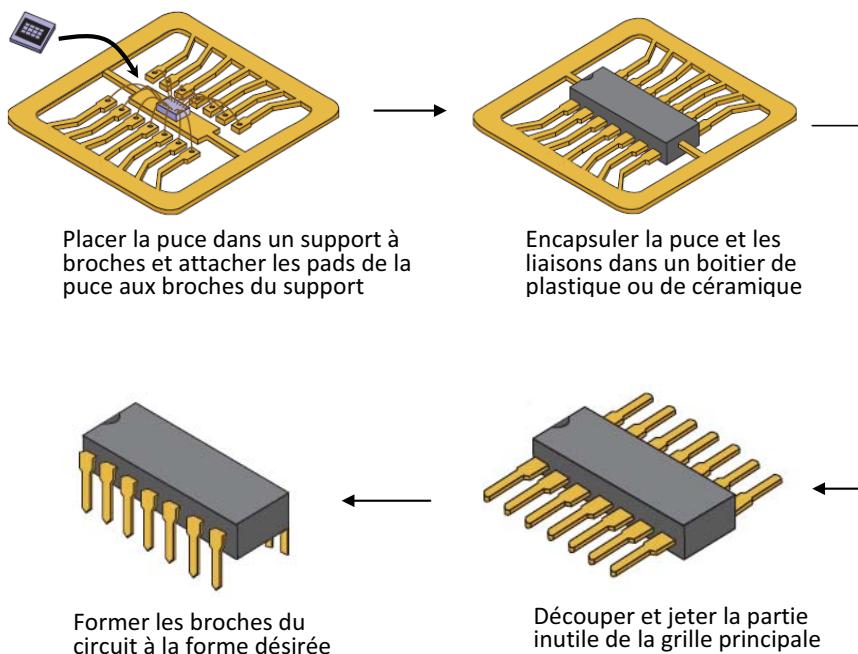

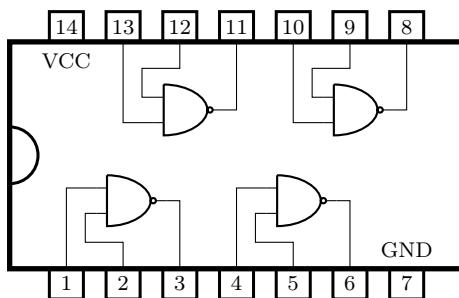

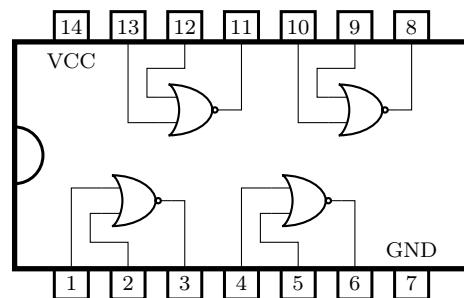

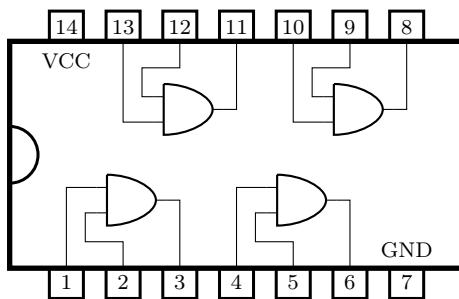

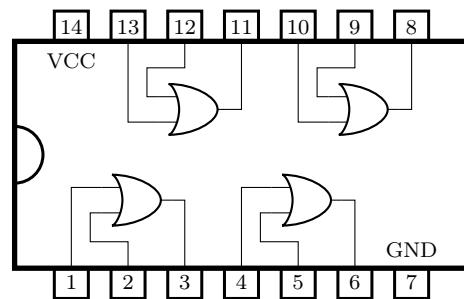

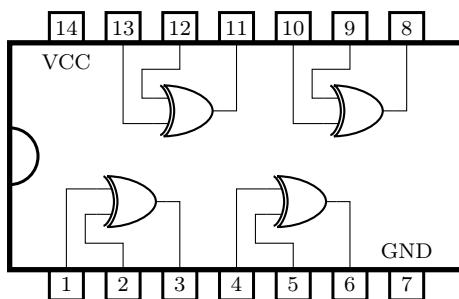

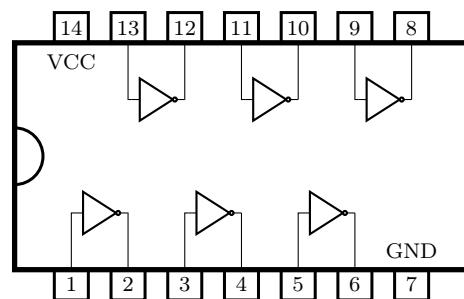

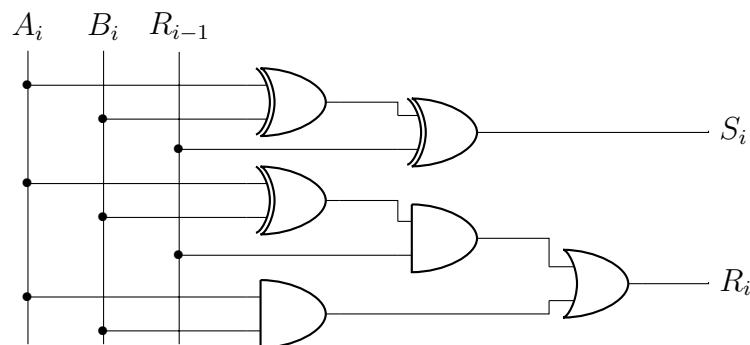

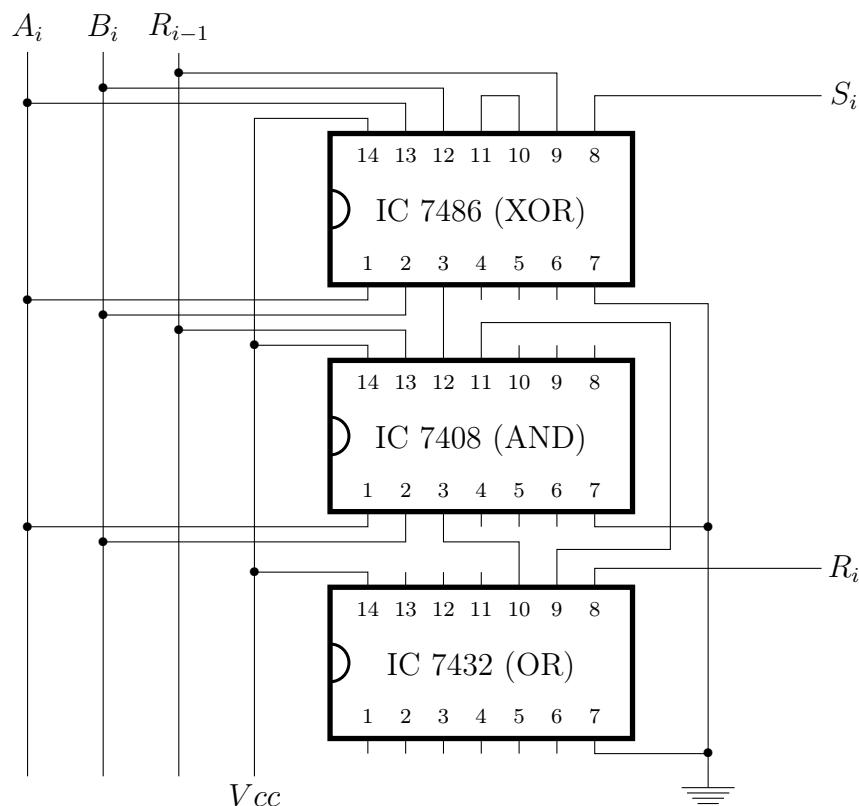

| 0                          | 1                                                                                   | 1                            |                                                                                                                                                                                                                                          |              |   |   |   |   |   |                                                                                       |   |   |   |   |   |   |   |   |                                                                                       |