## Chapitre IV : Les Circuits Séquentiels

### 1-Introduction :

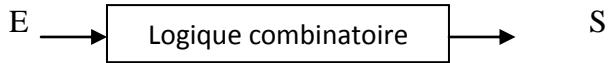

Comme nous avons vu dans les chapitres précédents, en logique combinatoire, pour une des combinaisons d'entrées, il existe une seule combinaison de la sortie (0 ou 1) qui est toujours la même. Une même action sur les entrées entraîne le même résultat sur la sortie.

Dans un système séquentiel, l'état des sorties dépend en plus de l'Histoire (de l'état précédent) la correspondance entre l'ensemble des entrées et l'état des sorties est Variables

Soient :  $F(t)$  : la valeur de la sortie du système à l'instant  $t$

$F(t+1)$  : la valeur de la sortie du système à l'instant  $t+1$

Alors :  $F(t+1) = fct(E, F(t))$

La sortie à l'instant  $t+1$  dépend de l'entrée  $E$  et de la sortie à l'instant  $t$

### 2-Bascule bistable :

La fonction la plus élémentaire que peut réaliser un circuit séquentiel est la fonction mémoire. On va étudier tout d'abord le point mémoire élémentaire auquel on ajoute ensuite des commandes d'écriture.

Une bascule (Flip-Flop) a pour rôle de mémoriser une information élémentaire. C'est une mémoire à 1 bit. Une bascule possède deux sorties complémentaires  $Q$  et  $\bar{Q}$ .

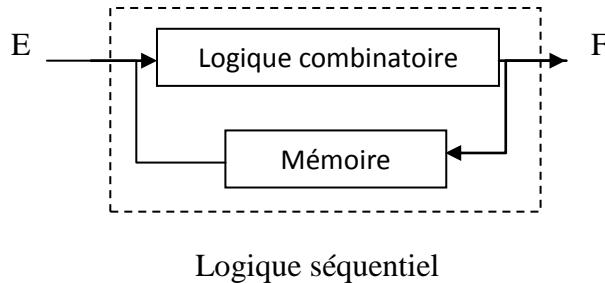

### 2-1 Le Point Mémoire Élémentaire :

La fonction mémoire sous sa forme la plus élémentaire est obtenue en connectant deux inverseur Tête- Bêche. Le rebouclage des deux portes confère à ce circuit son caractère séquentiel et permet de stocker une valeur logique. Ce circuit permet de mémoriser deux états possibles :

- 1-  $Q=0$  et  $\bar{Q}=1$

- 2-  $Q=1$  et  $\bar{Q}=0$

On peut vérifier :  $(Q=1) \Rightarrow (B=1) \Rightarrow (\bar{Q}=0) \Rightarrow (A=0) \Rightarrow (Q=1)$

$(Q=0) \Rightarrow (B=0) \Rightarrow (\bar{Q}=1) \Rightarrow (A=1) \Rightarrow (Q=0)$

Une bascule ne peut donc être que dans deux états : « 1 » ( $Q=1$  et  $\bar{Q}=0$ ) et « 0 » ( $Q=0$  et  $\bar{Q}=1$ ). Les interconnexions du verrou interdisent les deux autres combinaisons :  $Q=\bar{Q}=1$  ou  $Q=\bar{Q}=0$ . Ce type de circuit, qui n'a que deux états stables possibles est encore appelé circuit **BISTABLE**. Ce bistable constitué la base de la structure des mémoires.

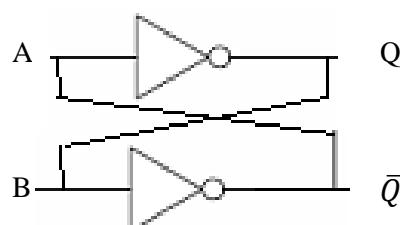

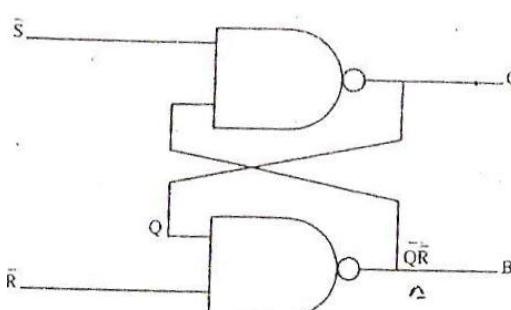

## 2-2 Bascule R-S (Reset –Set) :

Une évolution de la structure du bistable, appelée **Bascule RS** permet de rendre le bistable inscriptible.

**S : Set** : Mise à 1 ou information à mémoriser

**R : Reset** : mise à 0 ou effacer l'information

C'est la bascule de base qui sert à fabriquer les autres.

### Cahier des charges de la bascule R-S :

- Si, on applique aucun signal sur les entrées S et R ( $S=R=0$ ), la bascule conserve son état précédent.

- Si, on applique signal sur l'entrée S (la mise à 1) et rien sur l'entrée R (mise à 0) donc ( $S=1$  et  $R=0$ ), la bascule passe à 1 quelle que soit son état antérieur (état précédent).

- Si, on applique signal sur l'entrée R (la mise à 0) et rien sur l'entrée S (mise à 1) donc ( $S=0$  et  $R=1$ ), la bascule passe à 0 quelle que soit son état antérieur.

- L'application simultanée des deux signaux sur R et S ( $S=1$  et  $R=1$ ) est logiquement interdite.

| S | R | Q | $Q^+$ |

|---|---|---|-------|

| 0 | 0 | 0 | 0     |

| 0 | 0 | 1 | 1     |

| 0 | 1 | 0 | 0     |

| 0 | 1 | 1 | 0     |

| 1 | 0 | 0 | 1     |

| 1 | 0 | 1 | 1     |

| 1 | 1 | 0 | X     |

| 1 | 1 | 1 | X     |

Conserve l'état précédent

La mise à zéro

La mise à un

Etat indéterminé

$$Q^+ = S + \bar{R}Q \text{ d'où : } Q^+ = \bar{S} \cdot \bar{R}Q$$

Première forme avec les portes NAND

| Q SR | 00 | 01 | 11 | 10 |

|------|----|----|----|----|

| 0    | 0  | 0  | x  | 1  |

| 1    | 1  | 0  | x  | 1  |

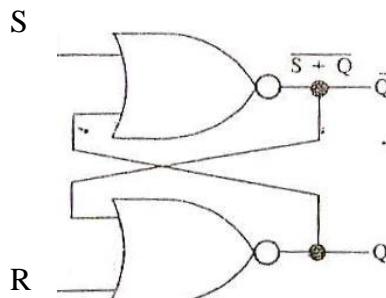

Logigramme

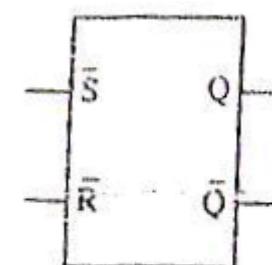

symbole logique (CI 74279)

Deuxième forme avec les porte NOR

$$Q^+ = \bar{R}(S+Q) \text{ d'où : } Q^+ = \overline{R + \overline{S} + \overline{Q}}$$

| Q\SR | 00 | 01 | 11 | 10 |

|------|----|----|----|----|

| 0    | 0  | 0  | x  | 1  |

| 1    | 1  | 0  | x  | 1  |

La table de vérité ci-dessous résume son fonctionnement :

| S | R | Q <sup>+</sup> |

|---|---|----------------|

| 0 | 0 | Q              |

| 0 | 1 | 1              |

| 1 | 0 | 0              |

| 1 | 1 | X              |

Conserve l'état précédent

La mise à zéro

La mise à un

Etat indéterminé

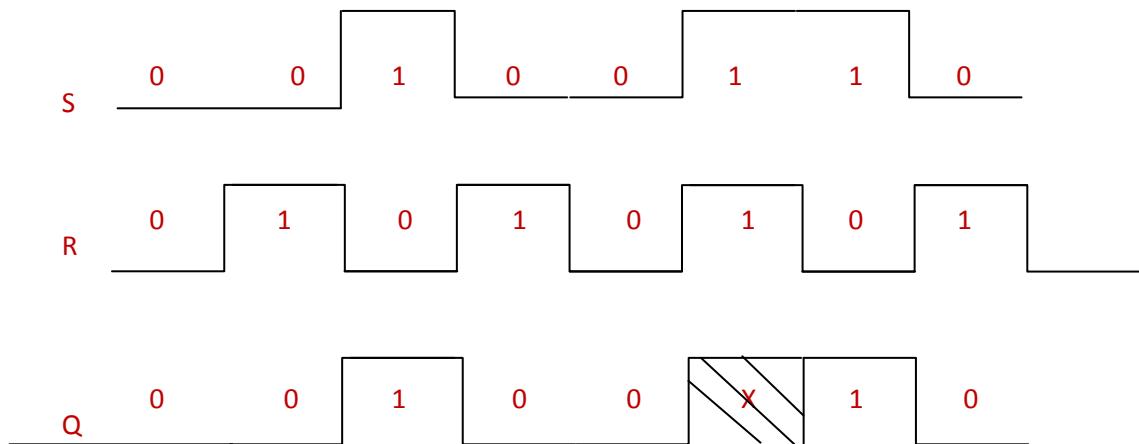

Exemple d'un chronogramme pour la bascule R-S :

| Q | S | R | Q <sup>+</sup> |

|---|---|---|----------------|

| 0 | 0 | 0 | 0              |

| 0 | 0 | 1 | 0              |

| 0 | 1 | 0 | 1              |

| 0 | 1 | 1 | θ              |

| 1 | 0 | 0 | 1              |

| 1 | 0 | 1 | 0              |

| 1 | 1 | 0 | 1              |

| 1 | 1 | 1 | θ              |

| S | R | Q <sup>+</sup> |

|---|---|----------------|

| 0 | 0 | Q              |

| 0 | 1 | 0              |

| 1 | 0 | 1              |

| 1 | 1 | θ              |

| Transition     | Q | Q <sup>+</sup> | S | R |

|----------------|---|----------------|---|---|

| S <sub>0</sub> | 0 | 0              | 0 | θ |

| T <sub>1</sub> | 0 | 1              | 1 | 0 |

| T <sub>0</sub> | 1 | 0              | 0 | 1 |

| S <sub>1</sub> | 1 | 1              | θ | 0 |

La Table de vérité de R-S

La TV réduite de R-S

Table des transitions de R-S

## 2-3-a Bascules asynchrones, ou verrous (désigné en anglais par le terme latch ou latched)

Ce sont des bascules dont la sortie ou l'état de mémorisation dépend à tout instant de l'état simultané des entrées. **Cette évolution ne dépend que de la succession des combinaisons appliquées**, et n'est limitée que par la vitesse de commutation de la bascule et de ses entrées, tandis qu'une bascule synchrone évolue au rythme du signal d'horloge. Si les entrées ont des oscillations imprévisibles avant de **se stabiliser**, la sortie d'une bascule asynchrone pourra être modifiée selon cette combinaison, alors qu'une bascule synchrone ne tiendra compte que des valeurs à la réception du signal d'horloge. **Le fait de synchroniser la bascule** sur les pulsations d'une horloge permet de s'assurer que sa sortie est bien stabilisée.

## 2-3-b Bascule R-S Synchrone (Flip-Flop)

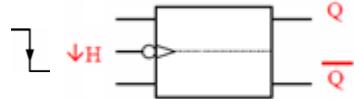

Dans une bascule R-S asynchrone, les ordres appliqués aux entrées R et S provoquent, immédiatement, le changement d'état correspondant. Par contre, dans une **bascule R-S synchrone**, l'exécution de l'ordre n'intervient qu'avec l'**impulsion d'horloge**. Pour synchroniser ce type de bascule, il suffit de valider les entrées R et S par une **horloge (H)** et, faire en sorte que lorsque **H=0**; les entrées n'ont aucun effet sur l'état de la bascule (état précédent). Dans cette théorie, nous examinerons par la suite la bascule R-S et ses dérivées, la bascule J-K, la bascule D et la bascule T commandées par une horloge.

| S | R | H | $Q^+$ |

|---|---|---|-------|

| 0 | 0 | 0 | Q     |

| 0 | 0 | 1 | Q     |

| 0 | 1 | 0 | Q     |

| 0 | 1 | 1 | 0     |

| 1 | 0 | 0 | Q     |

| 1 | 0 | 1 | 1     |

| 1 | 1 | 0 | X     |

| 1 | 1 | 1 | X     |

Conserve l'état précédent

Mise à zéro

Etat précédent

Mise à un

Etat indéterminé

Interdite

Horloge

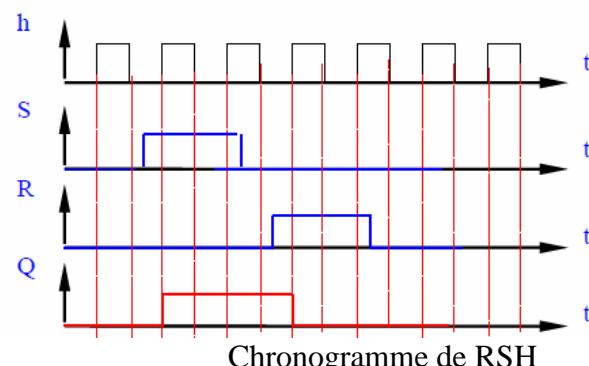

Bascule R-S synchrone (RSH)

| H | R | S | $Q^+$ | $\bar{Q}^+$ |

|---|---|---|-------|-------------|

| 1 | 0 | 0 | Q     | $\bar{Q}$   |

| 1 | 0 | 1 | 1     | 0           |

| 1 | 1 | 0 | 0     | 1           |

| 1 | 1 | 1 | X     | X           |

| 0 | X | X | Q     | $\bar{Q}$   |

Table de Vérité RSH

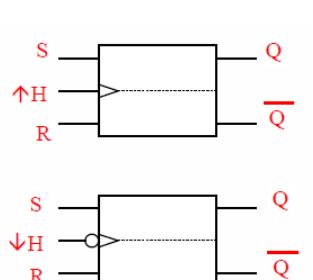

Symboles de RSH ( $\neq$ horloge)

Chronogramme de RSH (front montant)

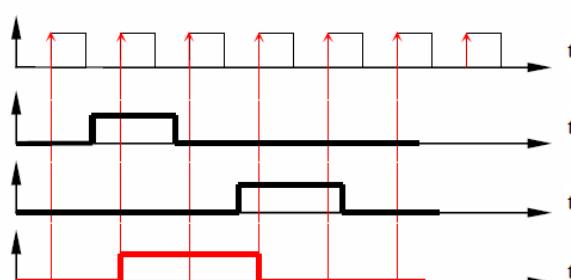

### 2-3 Bascule D (Data flip-flop) :

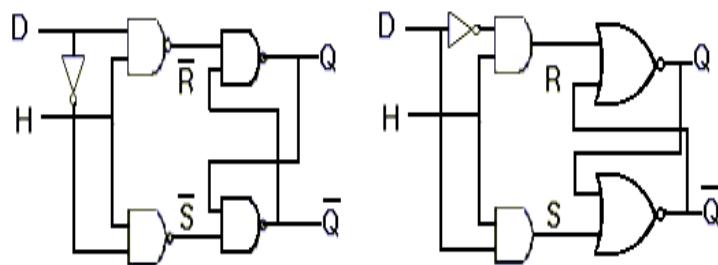

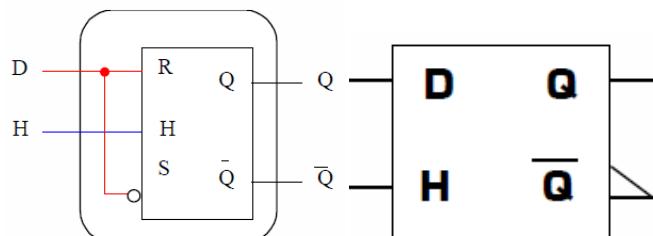

La bascule **D** est dérivée de la bascule **R.S.H.** Elle possède, quant à elle, une seule entrée «**D**» pour positionner les sorties. Pour cela on place un inverseur entre l'entrée **S** et l'entrée **R** de la bascule **R.S.H.** L'entrée **S** devient l'entrée **D** de la bascule.

Logigramme de la Bascule D

Symbole logique (CI 7474)

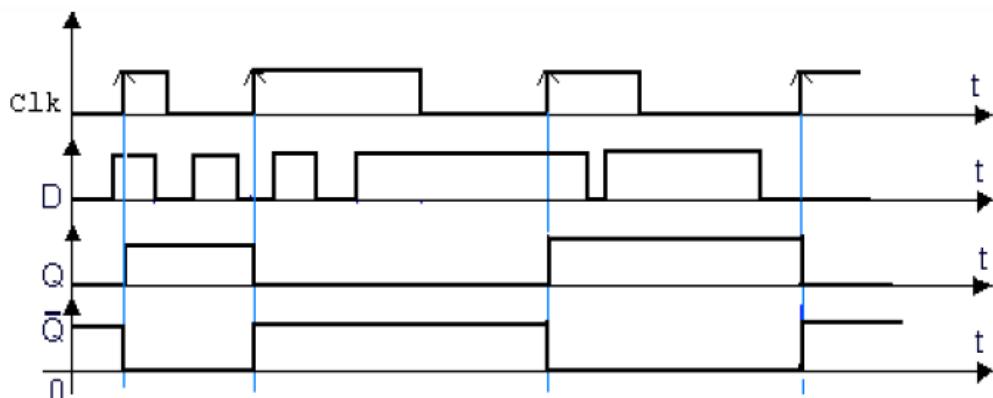

À chaque impulsion de **H**, la sortie de la bascule «recopie» l'état appliqué à l'entrée, notée **D**

| D | H | $Q_+$ | $\bar{Q}_+$ |

|---|---|-------|-------------|

| 1 | 0 | Q     | $\bar{Q}$   |

| 1 | 1 | 1     | 0           |

| 0 | 0 | Q     | $\bar{Q}$   |

| 0 | 1 | 0     | 1           |

La Table de vérité de D

| Transition | Q | $Q_+$ | D |

|------------|---|-------|---|

| S0         | 0 | 0     | 0 |

| T1         | 0 | 1     | 1 |

| T0         | 1 | 0     | 0 |

| S1         | 1 | 1     | 1 |

Table des transitions de D

Chronogramme de D normale (front montant)

**NB :** C'est le composant de base d'une mémoire d'ordinateur : est mis à 1 ou à 0 au moment voulu et figé le reste du temps.

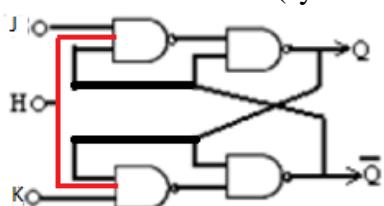

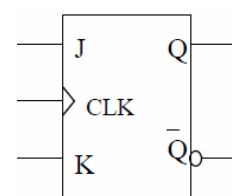

## 2-4 Bascule JK (flip-flop) :

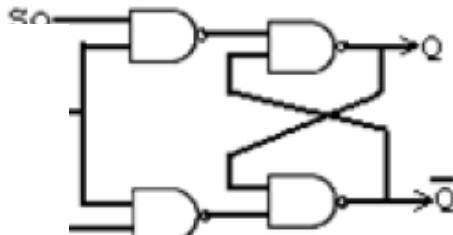

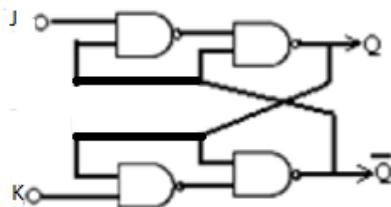

La bascule JK synchrone (Jack King) est obtenue à partir d'une bascule RS H dont les sorties sont rebouclées sur les entrées. Ceci permet **d'éliminer l'état indéterminé**.

C'est la bascule la plus utilisée et la plus importante, elle permet de réaliser les trois bascules (R-S, D et T) selon la connexion appropriée. La bascule JK

| J | K | Q | $Q^+$ |

|---|---|---|-------|

| 0 | 0 | 0 | 0     |

| 0 | 0 | 1 | 1     |

| 0 | 1 | 0 | 0     |

| 0 | 1 | 1 | 0     |

| 1 | 0 | 0 | 1     |

| 1 | 0 | 1 | 1     |

| 1 | 1 | 0 | 1     |

| 1 | 1 | 1 | 0     |

Conserve l'état précédent

La mise à zéro

La mise à un

Basculement

| J | K | $Q^+$     |

|---|---|-----------|

| 0 | 0 | Q         |

| 0 | 1 | 1         |

| 1 | 0 | 0         |

| 1 | 1 | $\bar{Q}$ |

| QJK | 00 | 01 | 11 | 10 |

|-----|----|----|----|----|

| 0   | 0  | 0  | 1  | 1  |

| 1   | 1  | 0  | 0  | 1  |

Equations caractéristiques :

$$Q^+ = J\bar{Q} + \bar{K}Q \text{ d'où : } Q^+ = \overline{J\bar{Q} + \bar{K}Q}$$

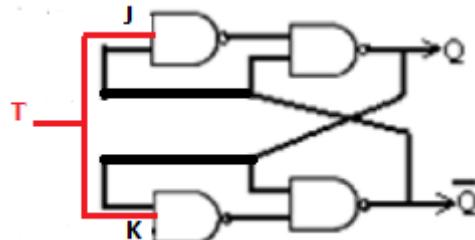

Bascule JK asynchrone

| Transition | Q | $Q^+$ | K | J |

|------------|---|-------|---|---|

| S0         | 0 | 0     | 0 | 0 |

| T1         | 0 | 1     | 0 | 1 |

| T0         | 1 | 0     | 1 | 0 |

| S1         | 1 | 1     | 0 | 0 |

Table des transitions de JK

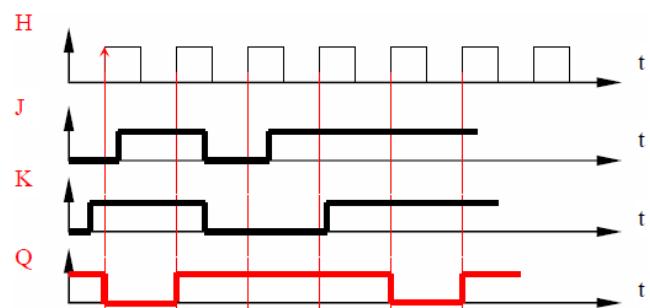

La bascule JK c'est une bascule synchrone, car la commutation possible de la sortie lorsque ( $J=K=1$ , problème de basculement) peut provoquer un cycle continu de commutations quand la durée des signaux appliqués est supérieur au temps de commutation de la mémoire. Pour cette raison, la durée sur les entrées J et K doit être très brève (rapide) pour éviter l'apparition de ce cycle. En réalité, il est difficile d'engendrer et de contrôler les impulsions de commande dont la durée soit inférieure au temps de commutation de la Bascule. Donc on introduit une troisième entrée de synchronisation H (Horloge, CLK) qui permet de donner une durée fixe à l'application des entrées J et K.

| H | J | K | $Q_n$           | $\bar{Q}_n$     |

|---|---|---|-----------------|-----------------|

| 0 | X | X | $Q_{n-1}$       | $\bar{Q}_{n-1}$ |

| ↑ | 0 | 0 | $Q_{n-1}$       | $\bar{Q}_{n-1}$ |

| ↑ | 0 | 1 | 0               | 1               |

| ↑ | 1 | 0 | 1               | 0               |

| ↑ | 1 | 1 | $\bar{Q}_{n-1}$ | $Q_{n-1}$       |

Table de vérité de JK (synchrone)

chronogramme de JK synchrone (front montant)

Logigramme JK H

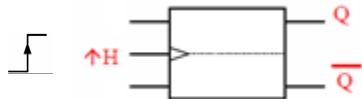

Symbol logique JK (CI 7473)

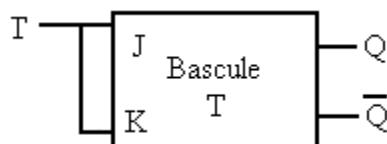

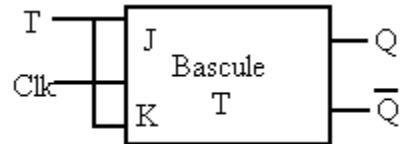

## 2-4 Bascule T (Trigger flip-flop) :

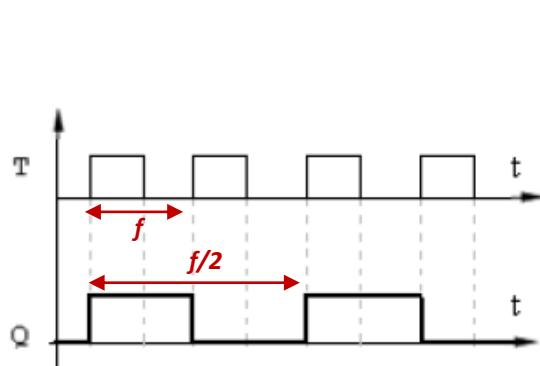

La sortie de la bascule T s'inverse pour chaque impulsion appliquée à l'entrée T. Il constitue un diviseur par deux puisque deux impulsions successives appliquées à l'entrée n'en fourniront qu'une à la sortie. C'est pourquoi on le qualifie de «**DIVISEUR BINAIRE**». Il peut être doté d'une entrée horloge qui peut le faire changer d'état à son rythme.

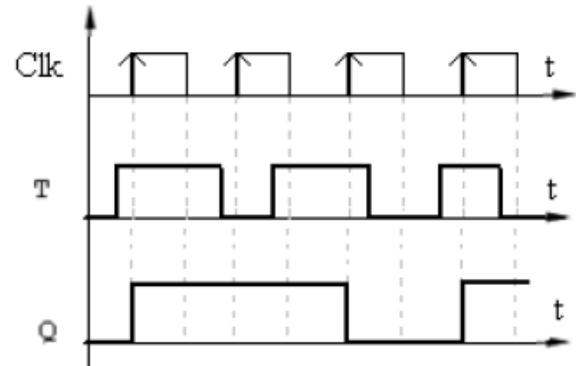

La bascule T s'obtient à partir de la bascule J-K en injectant le même signal dans les entrées J et K ( $T=J=K$ ). Cette bascule peut être **dotée d'une entrée Horloge**. Les chronogrammes de ces deux types de bascules sont donnés comme suit :

Bascule T

Bascule T synchrone

| T | Q | $Q^+$ |

|---|---|-------|

| 0 | 0 | 0     |

| 0 | 1 | 1     |

| 1 | 0 | 1     |

| 1 | 1 | 0     |

Conserve l'état précédent

(Ne fonction pas)

Inversion

(Etat opposé)

| T | $Q^+$     |

|---|-----------|

| 0 | Q         |

| 1 | $\bar{Q}$ |

Table de vérité de T

L'équation caractéristique :  $Q^+ = T \oplus Q$

Logigramme de T

Comme la bascule T a la propriété de basculer à chaque impulsion d'horloge, elle réalise donc une division de fréquence par 2 (comme montre la figure); elle servira aussi de base à la réalisation de compteurs (association simple si actives au front descendant de l'horloge).

Chronogrammes de la bascule T

Chronogrammes de la bascule T synchrone

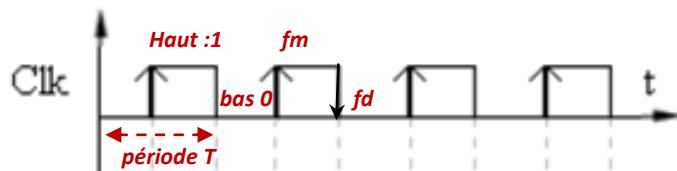

**Remarque :** En réalité l'activation se fait souvent sur le front montant (*fm*) ou descendant (*fd*) de la bascule (les changements d'état ne sont possibles que sur les actifs de l'horloge).

Horloge H(Ck) active au niveau haut (1)

Horloge H (Ck) active au niveau bas (0)

Les bascules sont actives au *niveau BAS* et sont représentées sur le schéma synoptique par *un petit cercle* (celles qui sont actives au *niveau HAUT* n'ont pas de petit cercle).

Ce signal d'horloge est un signal carré de période définie.

**Fig.** Signal d'horloge

### 3- Les Entrées asynchrones (de forçage)

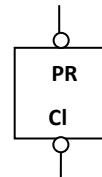

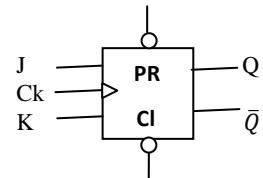

Les entrées des bascules précédemment discutées, SR, D, JK et T sont appelées des **entrées synchrones** parce que les données qu'elles portent ne sont transférées vers la sortie que lors du front déclencher du signal d'horloge. En d'autres termes, le transfert des données est synchronisé par le signal d'horloge. La plupart des CI de bascules sont également munis d'entrées **asynchrones**. Ces entrées permettent d'affecter l'état de la bascule **indépendamment** du signal d'horloge. Ces entrées sont appelées aussi **les entrées de forçage** ou de **prépositionnement** permettant la mise à 1 ou à 0 quelque soit l'état de la bascule.

Preset (PR) : la mise à 1 forcé

Clear (CI) : la mise à 0 forcé

Les entrées Preset et Clear sont prioritaires sur les entrées synchrones et souvent actives au niveau bas

- $PR=0 \Rightarrow$  la mise à 1,  $PR=1 \Rightarrow$  Prest est inactive

- $CI=0 \Rightarrow$  la mise à 0,  $CI=1 \Rightarrow$  Clear est inactive

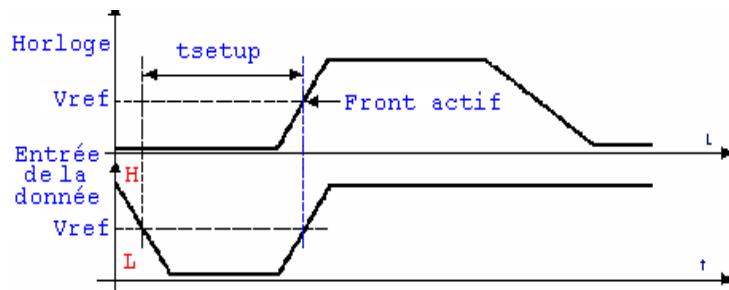

#### - Temps de prépositionnement (Set Up Time)

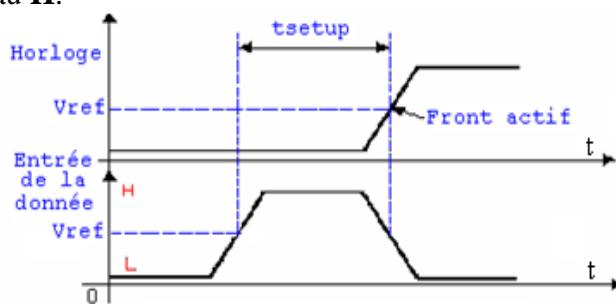

Le **temps de prépositionnement** est le temps minimal pendant lequel la donnée présente sur l'entrée doit rester stable avant le front actif du signal d'horloge pour que celle-ci soit reconnue. Si ce temps n'est pas respecté, la donnée ne sera pas prise en compte par le circuit.

La figure suivante illustre le temps de prépositionnement ( $t_{SETUP}$ ) lorsque la donnée à mémoriser est au niveau **L**.

Fig. Temps de prépositionnement d'une donnée au niveau **Low (Bas)**

$V_{ref}$  correspond à la tension de basculement des portes du circuit :

$V_{ref} = 1,5 \text{ V}$  en technologie TTL standard.

$V_{ref} = 1,3 \text{ V}$  en technologie TTL - LS.

$V_{ref} = V_{DD}/2$  en technologie C.MOS,  $V_{DD}$  étant la tension d'alimentation du circuit.

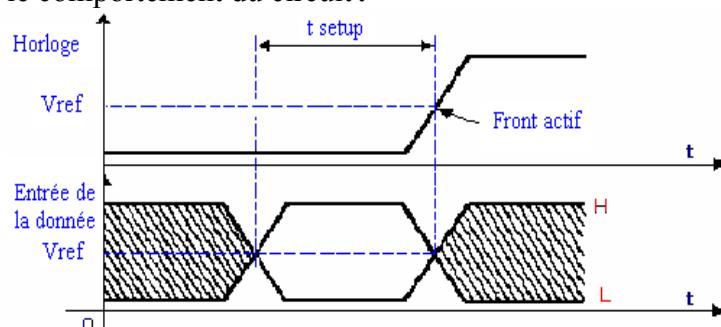

La figure ci- d'après illustre le temps de prépositionnement lorsque la donnée à mémoriser est au niveau **H**.

Fig. Temps de prépositionnement d'une donnée au niveau **Haut**

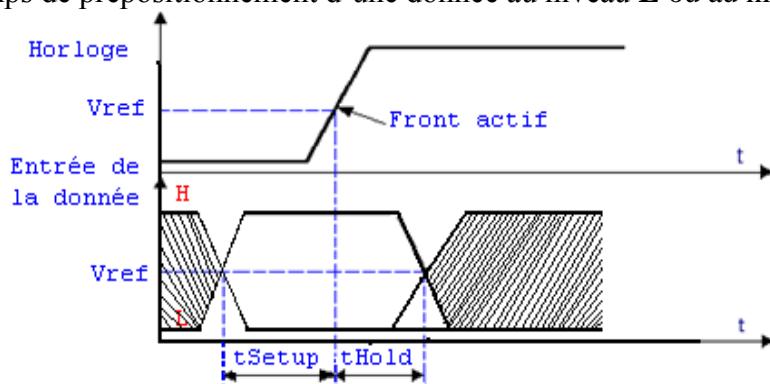

Les deux chronogrammes des figures précédentes sont souvent réunis en un seul dans les catalogues de constructeurs, comme le montre la figure suivante.

Les périodes hachurées indiquent que la donnée peut varier d'un niveau à l'autre sans qu'il n'y ait d'influence sur le comportement du circuit.

Fig. Temps de prépositionnement d'une donnée au niveau **L** ou au niveau **H**.

Fig. Temps de prépositionnement (**tsetup**) et de maintien (**tHold**).

**NB :** Pour obtenir un fonctionnement correct du circuit utilisé il faudra respecter un certains nombre de paramètres dont les principaux sont: *le temps de prépositionnement (SET UP TIME)*, *le temps de maintien (HOLD TIME)* et *le temps de propagation*.

### Exemple : (Bascule JK)

| Entrées asynchrones |    | Entrées synchrones |   |   | sortie |

|---------------------|----|--------------------|---|---|--------|

| PR                  | Cl | J                  | K | H | $Q^+$  |

| 0                   | 0  | X                  | X | x | $X(1)$ |

| 0                   | 1  | X                  | X | x | 1      |

| 1                   | 0  | X                  | X | x | 0      |

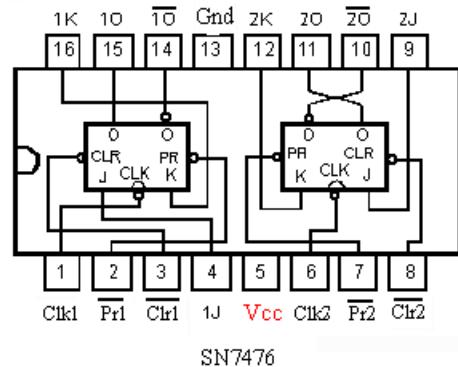

Le circuit intégré 74LS76 contient deux bascules JK S« H à front descendant» avec Preset et Clear. Le schéma de brochage est donné par la suite et La table de vérité de chaque bascule JK est reportée à la table suivante.

| Entrées |        |       |   |   | Sortie    |

|---------|--------|-------|---|---|-----------|

| Clear   | Preset | Clock | J | K | $Q^+$     |

| 0       | 1      | X     | X | X | 0         |

| 1       | 0      | X     | X | X | 1         |

| 0       | 0      | X     | X | X | Interdit  |

| 1       | 1      | I     | 0 | 0 | $Q^+$     |

| 1       | 1      | I     | 1 | 0 | 1         |

| 1       | 1      | I     | 0 | 1 | 0         |

| 1       | 1      | I     | 1 | 1 | $\bar{Q}$ |

| 1       | 1      | 1     | X | X | $Q^+$     |

| 1       | 1      | 0     | X | X | $Q^+$     |

Table de vérité de la bascule J-K et Schéma de brochage du circuit CI : SN7476

### 2- Bascule D

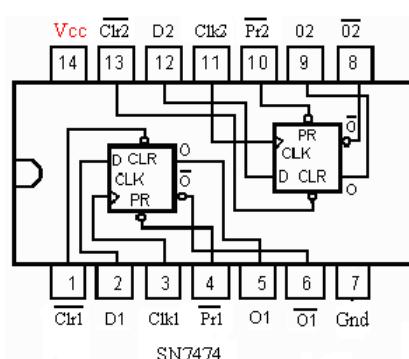

Le circuit intégré **SN 7474** contient 2 bascules **D** «H à front montant » indépendantes. La table de vérité de chaque bascule **D** est donnée :

| Entrées |       |       |   | Sortie   |

|---------|-------|-------|---|----------|

| Preset  | Clear | Clock | D | $Q^+$    |

| 0       | 0     | X     | X | Interdit |

| 0       | 1     | X     | X | 1        |

| 1       | 0     | X     | X | 0        |

| 1       | 1     | I     | 0 | 0        |

| 1       | 1     | I     | 1 | 1        |

| 1       | 1     | 0     | X | $Q^+$    |

| 1       | 1     | 1     | X | $Q^+$    |

Fig. Table de vérité de la bascule D et Schéma de brochage CI : SN7474

- **Clear** : une impulsion sur cette entrée met à ZERO la bascule quelque soit l'état des entrées de donnée et d'horloge :  $Q = 0$

- **Preset** : une impulsion sur cette entrée met à UN la bascule quelque soit l'état des entrées de donnée et d'horloge:  $Q = 1$

- **Clock** : signal de *synchronisation*. Lorsque l'entrée clock est activée, la bascule prend en compte l'état appliqué sur les entrées de donnée.