## TD n°2: JFET en régime dynamique

### Exercice n°1

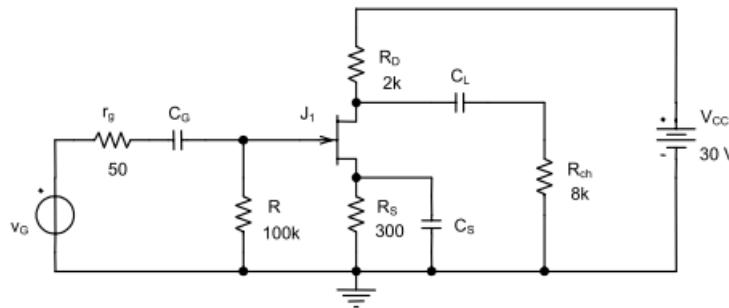

Le transistor à effet de champ du circuit suivant possède les caractéristiques  $I_{DSS} = 15 \text{ mA}$ ,  $V_P = -6 \text{ V}$ . La résistance  $R_{ch}$  représente la charge extérieure de l'étage. Les condensateurs ont une fonction de liaison (couplage).

### Etude du régime continu

1. Déterminez les points de fonctionnement du transistor.

### Etude du régime dynamique faibles signaux aux fréquences moyennes

2. Dessinez le schéma et évaluez le paramètre  $g_m$  du modèle du transistor ( $r_{ds}=\infty$ ).

3. Calculez la résistance d'entrée  $Z_e$  vue par le dipôle d'attaque ( $V_g$ ,  $r_g$ ).

4. Ecrivez les expressions des éléments du dipôle de Thévenin ( $v_{s0}$ ,  $Z_s$ ) du montage attaquant la charge  $R_{ch}$ .

5. Identifiez les éléments du quadripôle représentatif de l'amplificateur de tension, attaqué par le dipôle d'attaque et chargé par  $R_{ch}$ .

6. Evaluatez le transfert en tension  $V_s / V_g$

### Exercice n°2:

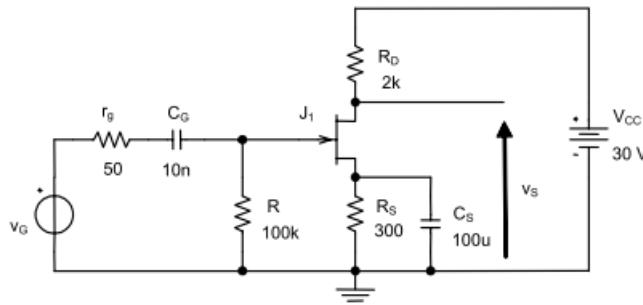

Le transistor à effet de champ du circuit suivant possède les caractéristiques statiques  $I_{DSS} = 15 \text{ mA}$ ,  $V_P = -6 \text{ V}$  et les paramètres de son modèle dynamique aux faibles signaux sont  $r_{ds} = \infty$ . Les composants  $C_G$  et  $C_S$  sont respectivement des condensateurs de liaison et de découplage.

### Etude du régime continu

1. Déterminez le point de repos du transistor.

### Etude du régime dynamique aux faibles signaux

2. Evaluatez le paramètre  $g_m$  du modèle du transistor de l'étude précédente.

3. Aux fréquences moyennes, calculez le gain en tension  $A_{V0} = V_S / V_G$ , les résistances d'entrée  $Z_e$  et de sortie  $Z_s$ .

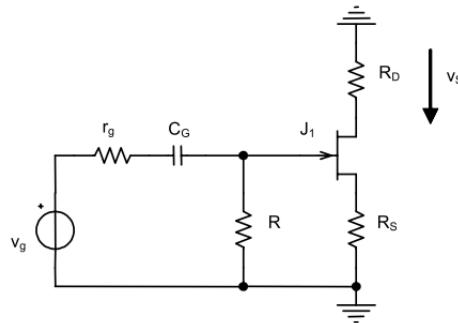

### Exercice n°3:

Le paramètre  $r_{ds}$  du modèle en comportement linéaire du transistor JFET est supposé de valeur très importante. Le composant  $C_G$  est un condensateur de liaison et la valeur de la résistance du dipôle d'attaque est telle que  $r_g \ll R$ .

### Etude du régime dynamique aux fréquences moyennes

1. Dessinez le schéma.

2. Ecrivez les expressions du gain en tension  $A_{V0} = V_S / V_G$  et des résistances d'entrée  $Z_e$  et de sortie  $Z_s$  du montage.

### Exercice n°4 (Etage différentiel à JFET)

Les deux transistors du montage sont supposés technologiquement identiques avec  $I_{DSS} = 2$  mA ,  $V_P = -2$  V.

#### Etude en régime continu

1. Evaluez les courants de drain des transistors.

#### Etude du régime dynamique faibles signaux aux fréquences moyennes

2. Déduisez de l'étude du régime continu, les valeurs des paramètres  $g_{mi}$  des transistors  $J_i$ .

3. Ecrivez l'expression de la résistance dynamique  $Z_0$  de la source de courant  $I_0$  vue entre le drain et la masse. Evaluez cette dernière, le paramètre  $r_{ds3}$  étant estimé à  $100$  k $\Omega$ .

4. Les paramètres  $r_{ds}$  des transistors  $J_1$  et  $J_2$  étant négligés, écrivez puis évaluez les gains en tension  $A_d = V_S / V_d$  et  $A_C = V_S / V_C$ .

5. Déduisez le  $T_{RMC}$  en dB.

6. Evaluatez les résistances différentielle  $Z_d$ , de mode commun  $Z_C$  et de sortie  $Z_S$  du montage.