## Série TD N°=1 Circuits Combinatoires

### Exercice 1

1. Réaliser un circuit qui effectue une soustraction 1bit par 1bit (un demi-soustracteur) :

- Tracer la table de vérité,

- Donner les équations de sortie,

- Etablir le schéma logique.

2. A partir du demi-soustracteur qui vient d'être réalisé, concevoir un soustracteur complet (1 bit par 1 bit avec retenue d'entrée).

3. Donner le schéma d'un soustracteur quatre bits par quatre bits.

### Exercice 2

Le but est de construire un circuit combinatoire **C1** pour la porte logique **XOR** à trois entrées **A, B, C** :

- Tracer la table de vérité,

- Donner le schéma logique du circuit **C1**.

En utilisant uniquement des circuits **C1**, réaliser le circuit de la fonction suivante :

$$F(A, B, C, D, E, F, G, H) = A \oplus B \oplus C \oplus D \oplus E \oplus F \oplus G \oplus H$$

### Exercice 3

Réaliser un circuit qui effectue la détection de débordement de capacité à l'issue d'un calcul entre 2 nombres **a** et **b**.

On suppose que : - **Sa** est le signe du nombre **a**,

- **Sb** est le signe du nombre **b**,

- **Sr** est le signe du résultat du calcul entre **a** et **b**.

On pourra affirmer qu'il y a débordement lorsque les signes de **a** et **b** (**Sa** et **Sb**) sont égaux et au même temps ils sont différents du signe du résultat (**Sr**).

### Exercice 4

1. Réaliser un circuit qui effectue la multiplication 1 bit par 1 bit.

2. Réaliser un multiplicateur 2 bits par 2 bits en suivant les mêmes étapes que celles de la première question.

3. Réaliser un multiplicateur 2 bits par 2 bits à partir du multiplicateur 1 bit par 1 bit réalisé dans la première question et de demi-additionneurs.

### Exercice 5

- Réaliser les circuits combinatoires qui permettent le passage du binaire (3bits) au code Gray, et inversement.

### Exercice 6

1. Donner l'expression de la sortie S d'un MUX (2×1) ayant deux entrées de données (e0, e1) et une entrée de commande c.

2. Exprimer chaque opérateur logique : Not, AND et OR par le minimum des multiplexeurs (2×1)

3. Soit la fonction logique F suivante :

$$F(A, B, C) = \bar{A}\bar{B} + \bar{A} \cdot C + \bar{B} \cdot C$$

- Réaliser la fonction F à l'aide d'un multiplexeur (8×1).

- Réaliser la fonction F à l'aide d'un multiplexeur (4×1).

- Réaliser la fonction F à l'aide d'un multiplexeur (2×1).

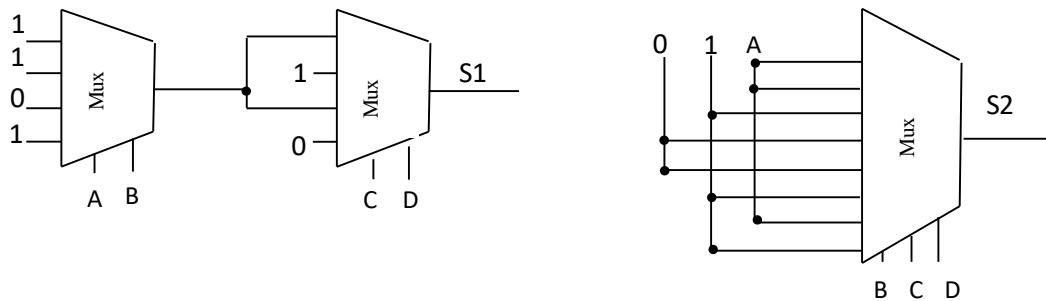

4. 'Déterminer l'expression logique de S1 et S2

### Exercice 7

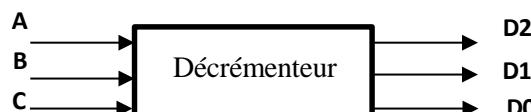

On désire réaliser un circuit pour un décrémenteur à 3 bits (le cas 000 est fixe ne change pas):

- Tracer la table de vérité.

- Réaliser la fonction **D2** à l'aide d'un MUX (8×1).

- Réaliser la fonction **D1** à l'aide d'un DEMUX (1×8).

- Réaliser la fonction **D0** à l'aide d'un MUX (4x1).

### Exercice 8

1. Réaliser les fonctions suivantes en utilisant uniquement des décodeurs (1×2), (2×4) et (3×8) et des portes logiques.

$$F(A, B, C) = \sum(0, 1, 4, 6, 7)$$

$$F(A, B, C, D) = \sum(0, 1, 5, 10, 12, 15)$$

$$F(A, B, C, D, E) = \sum(0, 2, 7, 11, 18, 22, 29, 31)$$

2. Soit la fonction logique F suivante :

$$F(A, B, C) = \bar{A}\bar{C} + \bar{A} \cdot B + \bar{B} \cdot C$$

- Réaliser la fonction F à l'aide d'un décodeur (3×8).

- Réaliser la fonction F à l'aide de deux décodeurs (2×4).

3. Donner le schéma logique d'un additionneur 2 bits qui fait l'addition A+B avec A=a1a0 et B=b1b0 en utilisant un décodeur (2×4) et décodeur (3× 8) et des portes logiques.