## Le transistor MOS

### 1/Introduction

---

Le transistor MOS est le composant le plus employé de nos jours. La première description du transistor IGFET (*Insulated Gate Field Effect Transistor*) a été réalisée en 1926 (Lilienfield). La première fabrication date de 1960 (Kaghn et Attala).

### 2/Définitions

---

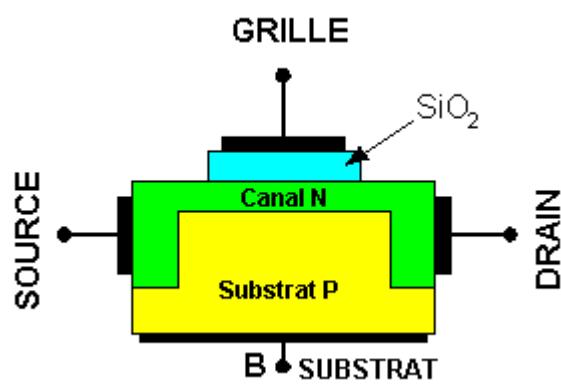

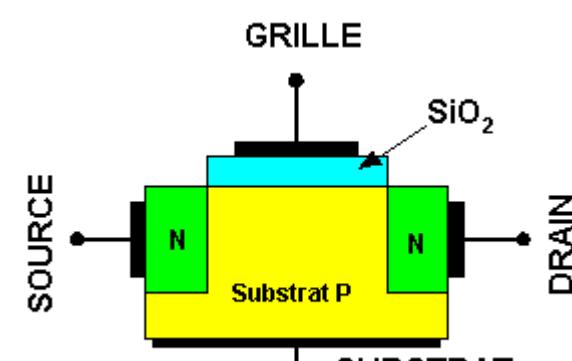

Le Transistor à Effet de Champ à Métal Oxyde Semiconducteur (**MOSFET** : *Metal Oxyde Semiconductor Field Effect Transistor*) a sa grille isolée du canal par une couche de dioxyde de silicium ( $\text{SiO}_2$  ).

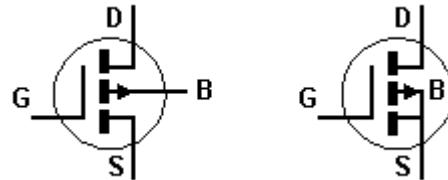

Le transistor MOS possède 4 électrodes : la Source (*Source*) **S**: point de départ des porteurs, le Drain (*Drain*) **D** :point de collecte des porteurs. La Grille (*Gate*) **G** et le Substrat (*Body*) **B** sont les électrodes de la capacité MOS qui contrôle **le nombre de porteurs présents dans le canal.**

L'intensité du courant circulant entre la source et le drain est commandée par la tension entre la grille et le substrat. Très souvent les électrodes de source et de substrat sont électriquement reliées, on retrouve un composant à 3 électrodes dans lequel la courant entre le **Drain** et la **Source**  $I_{DS}$  est commandé par une tension entre la **Grille** et la **Source** (potentiel de source = potentiel de substrat) :  $V_{GS}$ .

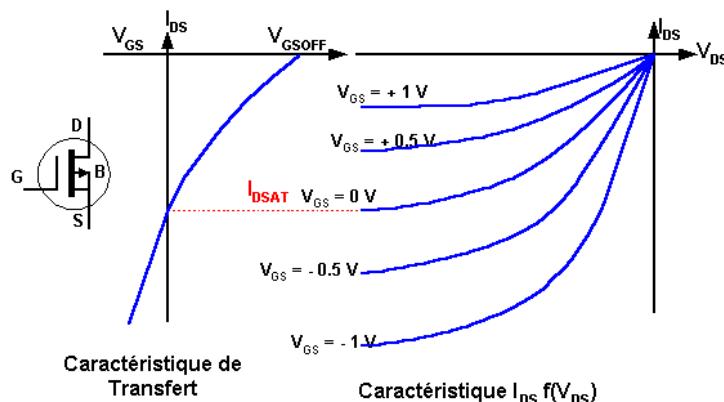

#### *Relation tension-courant*

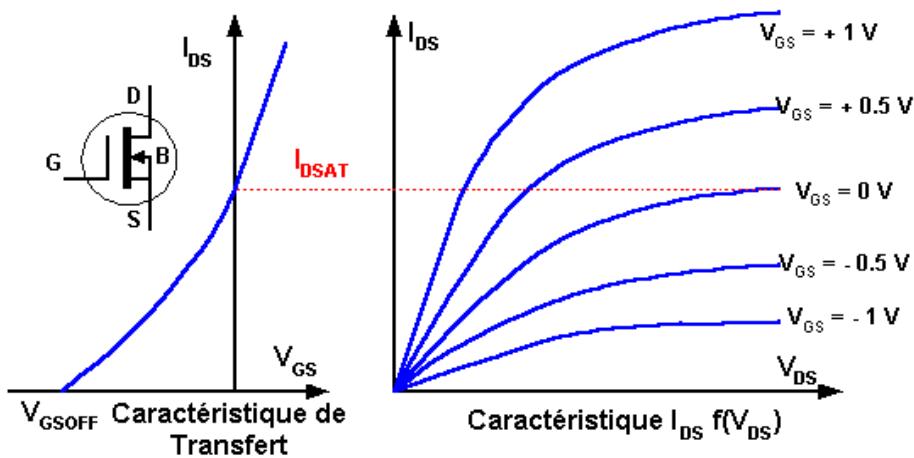

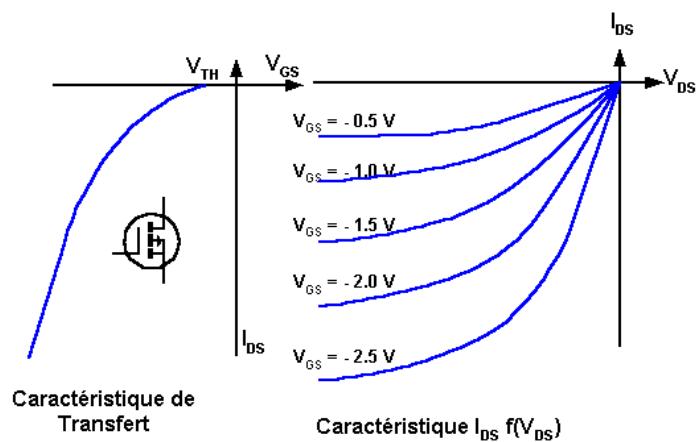

- Le courant dans entre le drain et la source est commandé par la tension grille-source.

- La tension entre grille et source peut être négative ou positive

- Une tension grille-source négative fait décroître le courant entre drain et source

- Une tension grille-source positive fait augmenter le courant entre drain et source

- Si la tension grille-source dépasse une valeur négative  $VT$  (appelée tension de pincement) le courant entre drain et source est interrompu

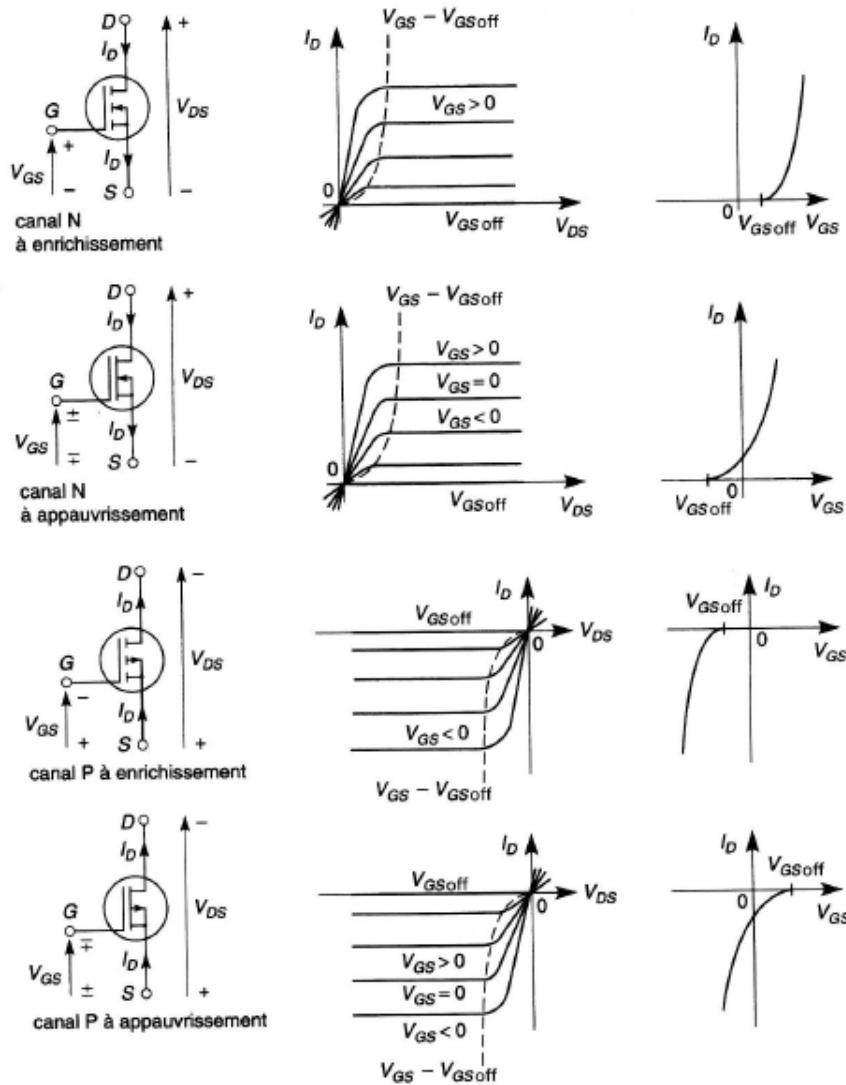

Les deux types fondamentaux de MOSFET sont les **MOSFET à appauvrissement** (Depletion) **D-MOSFET**, et les **MOSFET à enrichissement** (*Enhancement*) **E-MOSFET**.

Dans chaque type de MOSFET, on peut distinguer le **MOSFET canal N** (le courant provient du déplacement d'électrons) et le **MOSFET canal P** (le courant provient du déplacement de trous).

Dans les MOSFET, le type du canal (N ou P) ne correspond pas forcément au type du semiconducteur sous la grille.

### 3/Structure et fonctionnement

#### 3.1/MOS à appauvrissement D-MOS

##### 3.1.1/ Structure

**\*/Structure du MOS à appauvrissement canal N**

Le D-MOS le drain et la grille sont reliés par un canal étroit du même type : N pour D-MOS canal N.

##### Régime d'appauvrissement.

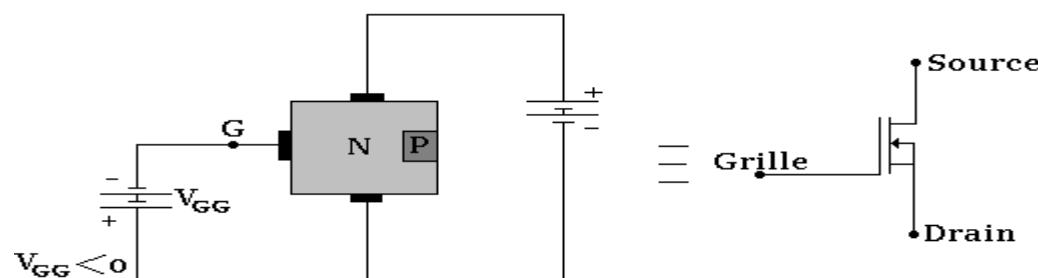

Dans le cas du D-MOS canal N, si on applique une tension négative sur la grille par rapport au substrat, les électrons sont repoussés et la conductivité du canal diminue.

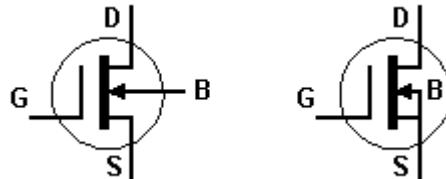

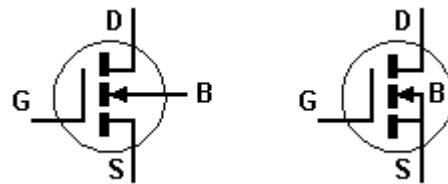

##### Représentation

**\*/Structure du MOS à appauvrissement canal P**

Le D-MOS le drain et la grille sont reliés par un canal étroit du même type : P pour D-MOS canal P.

##### Régime d'appauvrissement.

Dans le cas du D-MOS canal P, si on applique une tension positive sur la grille par rapport au substrat, les trous sont repoussés et la conductivité du canal diminue.

### Représentation

Les transistors MOS à appauvrissement sont passants sans tension de commande sur la grille (**NORMALLY ON**), ils deviennent de moins en moins conducteurs au fur et à mesure que la tension de commande augmente pour finalement se bloquer au delà d'une tension de blocage  $V_{GSoff}$ .

#### 3.1.2/Fonctionnement

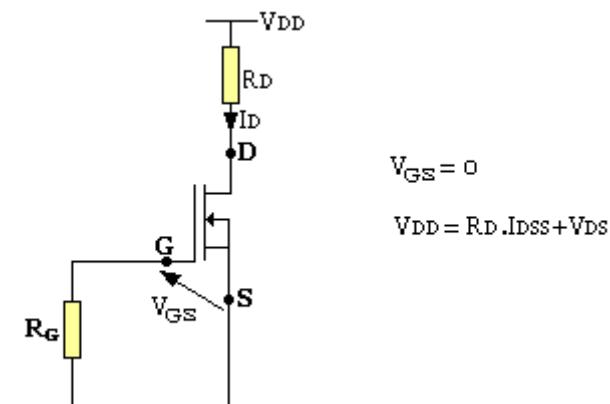

Sa polarisation est la même que celle d'un JFET. On peut donc distinguer la polarisation automatique, la polarisation par source de courant ici est conseillée. Cependant comme il peut aussi fonctionner en régime d'enrichissement, il convient de régler son point de repos Q à  $V_{GS}=0$ . On utilise alors un circuit de polarisation.

#### Régime d'appauvrissement du MOS à appauvrissement :

La grille est portée à un potentiel négatif, cette polarisation de la Grille contribue à réduire le canal à travers laquelle passent les électrons qui circulent de la source vers le Drain, plus la grille est négative. Ce fonctionnement du MOS est semblable à celui du JFET.

### Régime d'enrichissement du MOS à appauvrissement:

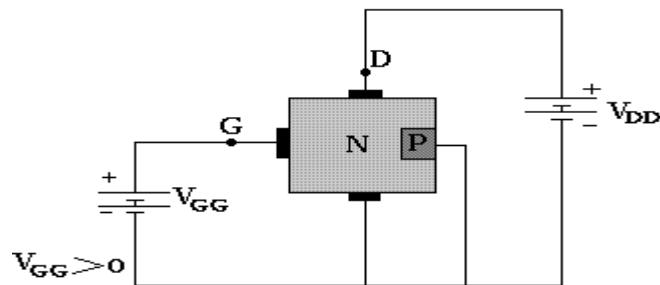

La Grille est portée à un potentiel positif, cette polarisation va augmenter le nombre d'électron libre qui traverse le canal, plus la tension de Grille est positive plus le courant de Drain est positif.

En raison de la couche isolante, un courant de Grille négligeable circule dans les deux régimes. C'est aussi que la résistance d'entrée d'un MOS est extrêmement grande.

Canal N : le courant entre la source et le drain est un courant d'électrons.

Canal P : le courant entre la source et le drain est un courant de trous.

Régime d'appauvrissement :

Canal N :  $V_{GS} < 0$

Canal P :  $V_{GS} > 0$

- Peut travailler en régime d'enrichissement.

- $V_{GS}$  commande  $I_{DS}$  (courant commandé par une tension).

- Blocage ( $I_{DS} = 0$ ) pour  $V_{GS} = V_{GSoff}$ .

- $I_{DSS}$  est obtenu pour  $V_{GS} = 0$

### 3.1.3/Application des MOS à déplétion

---

Une fois le MOS à déplétion polarisé à un point Q, il amplifie les petits signaux comme un JFET, et son schéma équivalent reste identique à celui d'un JFET en petits signaux. Ce MOS constitue aussi un amplificateur tampon idéal, car sa Grille isolé fait tendre sa résistance d'entrée à l'infini.

## 3.2/MOSFET à enrichissement : E-MOSFET

---

### 3.2.1/ Structure

---

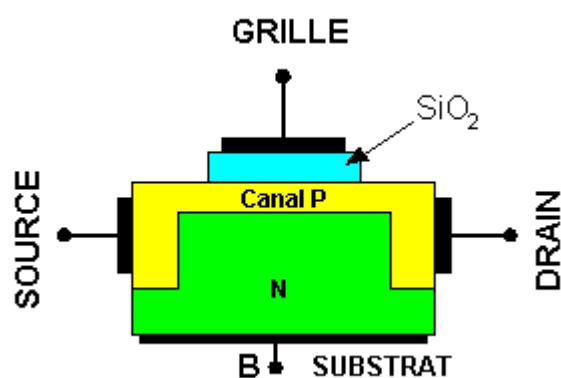

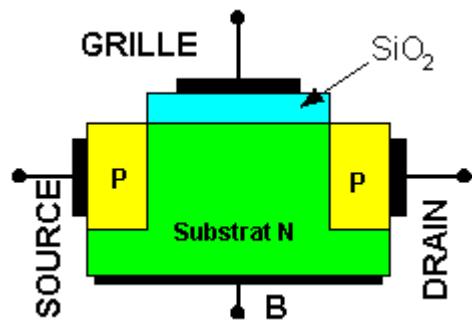

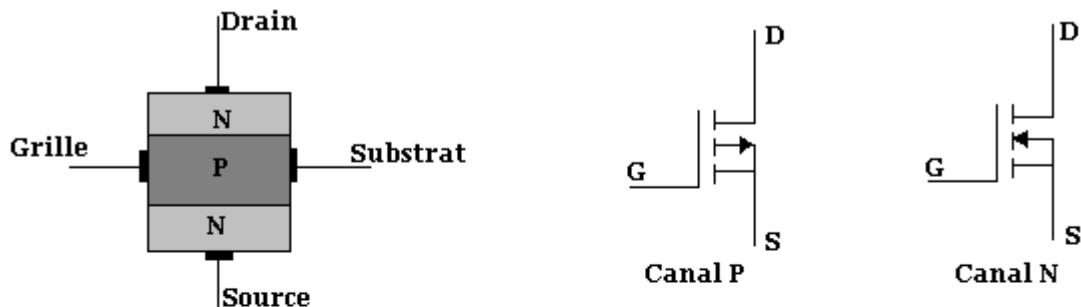

**\*/Structure du MOS à enrichissement** Le E-MOS le drain et la grille ne sont pas reliés par un canal du même type.

Sans tension de commande, le E-MOS est bloqué : **(NORMALLY OFF)**.

#### Régime d'enrichissement.

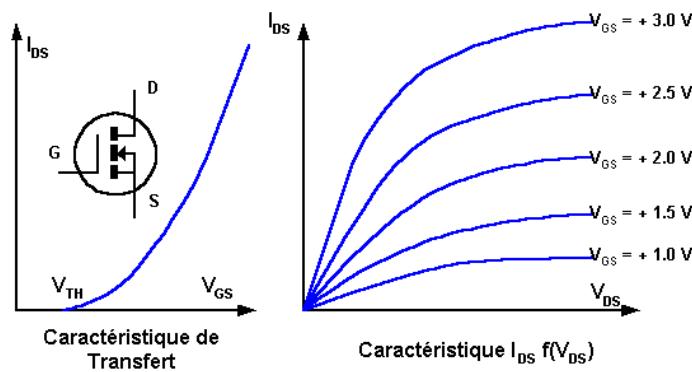

En appliquant une tension positive sur la grille, on attire les électrons à l'interface isolant-semiconducteur et on repousse les trous. A partir d'une certaine valeur : **tension de seuil  $V_{TH}$  (Threshold Voltage)**, une couche d'inversion apparaît et le transistor devient de plus en plus passant.

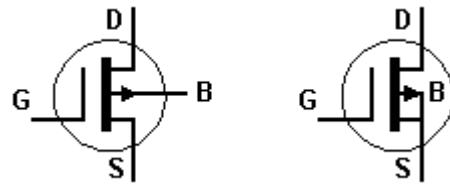

#### Représentation

**\*/Structure du MOS à enrichissement canal P**

E-MOS canal P

### Régime d'enrichissement.

Dans le cas du E-MOS canal P, si on applique une tension négative sur la grille par rapport au substrat, les électrons sont repoussés et les trous minoritaires sont attirés. A partir d'une certaine valeur : **tension de seuil  $V_{TH}$**  (*Threshold Voltage*), une couche d'inversion apparaît et le transistor devient de plus en plus passant.

### Représentation

Les transistors MOS à enrichissement sont bloqués sans tension de commande sur la grille (**NORMALLY OFF**), ils deviennent passants à partir d'une certaine tension de grille  $V_{TH}$ . Plus  $|V_{GS}| > |V_{TH}|$ , plus le E-MOS devient passant.

### 3.2.2/Fonctionnement

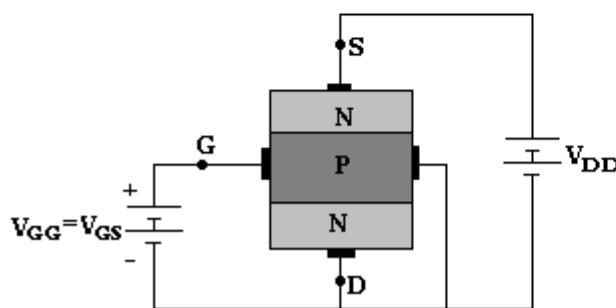

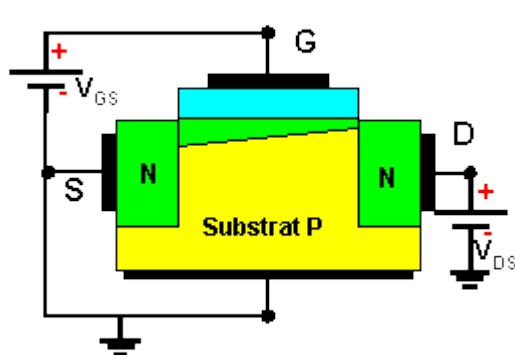

Dans un MOS à enrichissement, le substrat s'étend jusqu'à la couche du dioxyde de silicium, il y'a plus de canal entre le Drain et la Source.

#### Polarisation habituelle :

Lorsque  $V_{GS}=0$  la source  $V_{DD}$  tente de faire circuler les électrons de S vers D. Mais le substrat n'ayant que quelques porteurs minoritaires, le courant entre S et D est nul. C'est pour cette raison que le MOS à enrichissement est appelé *MOS normalement bloqué*. Lorsque  $V_{GS}>0$  la Grille et le substrat ressemblent à deux plaques d'un condensateur séparé par un isolant.

La Grille attire les électrons libres de S dans le point inférieur gauche de S dans le point inférieur gauche de la couche P. Si la Grille est suffisamment positive assez d'électrons sont attirés pour former une mince couche d'électron entre S et D. Ainsi un matériau du type N se forme près du  $\text{SiO}_2$ . On appelle cette couche d'électron libre la couche d'inversion du type N. La tension minimale  $V_{GS}$  qui crée la couche d'inversion du type N est appelée tension de seuil et notée  $V_{GS(\text{th})}$ . Si  $V_{GS} < V_{GS(\text{th})}$  alors  $i_D=0$ . Pour que la Grille commande mieux le courant Drain, la couche  $\text{SiO}_2$  doit être aussi mince que possible. Par ailleurs la tension  $V_{GS}$  ne doit pas dépasser une certaine valeur maximale appelée  $V_{GS\text{max}}$  sous peine de destruction. Pour cette raison, on protège certains MOS intérieurement par des Zener.

Cependant le type de polarisation propre au MOS à enrichissement est la polarisation à réaction de Drain. Quand le MOS conduit il y'a le courant Drain  $I_D$  passant.  $I_G=0$  ;  $V_{GS}=V_{DS}>0$  avec  $V_{GS}$  supérieur ou égale à  $V_{GS(\text{th})}$ . Arbitrairement la fiche technique donne la valeur de  $I_D$  passant pour  $V_{GS}=V_{GS(\text{passant})}$ . Pour un point de repos donné on choisit alors la valeur de  $R_D$   $R_D=(V_{DD}-V_{DS(\text{passant})})/I_{D(\text{passant})}$

Canal N : le courant entre la source et le drain est un courant d'électrons.

Canal P : le courant entre la source et le drain est un courant de trous.

● Régime d'enrichissement :

Canal N :  $V_{GS} > 0$

Canal P :  $V_{GS} < 0$

●  $V_{GS}$  commande  $I_{DS}$  (courant commandé par une tension).

● La valeur de  $V_{GS}$  pour laquelle le courant  $I_{DS}$  apparaît est la tension de seuil  $V_{TH}$ .

### 3.2.3/Application de MOS à enrichissement

En amplification dans la zone linéaire. (Etage d'entrée des AIL).

En commutation de puissance (plusieurs dizaines de Watts jusqu'à des fréquences de plusieurs milliers de mégahertz).

Les portes logiques CMOS.

Très utilisé en électronique numérique (mémoires, microprocesseurs, circuits logiques...)

### 3.3/Conventions et réseaux de caractéristiques

Donc on distingue deux types de transistors à effet de champ :

- MOS canal N (à enrichissement ou appauvrissement)

- MOS canal P (à enrichissement ou appauvrissement).

Rem. : Le transistor le plus utilisé est le MOSFET à enrichissement (Canal N).

| Avantages                                                                                                                                                                                                       | Inconvénients                                                                                                                                                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Consommation faible<br>Pas de courant de polarisation de grille.<br>Très forte impédance d'entrée (env. $10^{15} \Omega$ )<br>Peu onéreux.<br>Densité d'intégration importante ( $> 10^7$ transistors par puce) | Vitesse de commutation plus faible (sauf VMOS)<br>Dispersion des paramètres élevée.<br>Fragilité au niveau de la grille, extrêmement sensible aux charges électrostatiques qui peuvent provoquer le clacage de la couche de silice. |

Schéma équivalent pour les petites variations autour du point de repos.

## 4/Modèle du Transistor MOS (analyse du régime statique)

- le modèle linéaire : comportement du MOS pour de faibles tensions Drain-Source.

- le modèle quadratique : on tient compte de la variation de la charge d'inversion dans le canal entre la source et le drain.

On étudie un E-MOSFET canal N

Hypothèses simplificatrices :

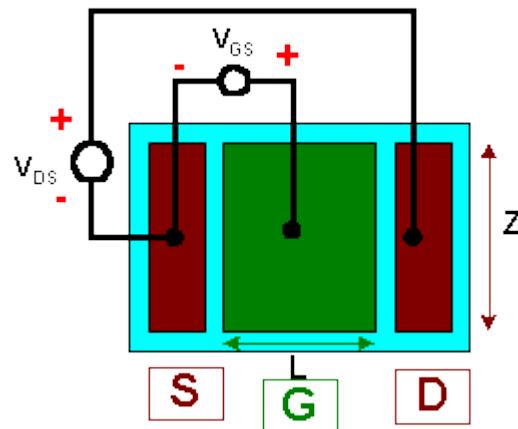

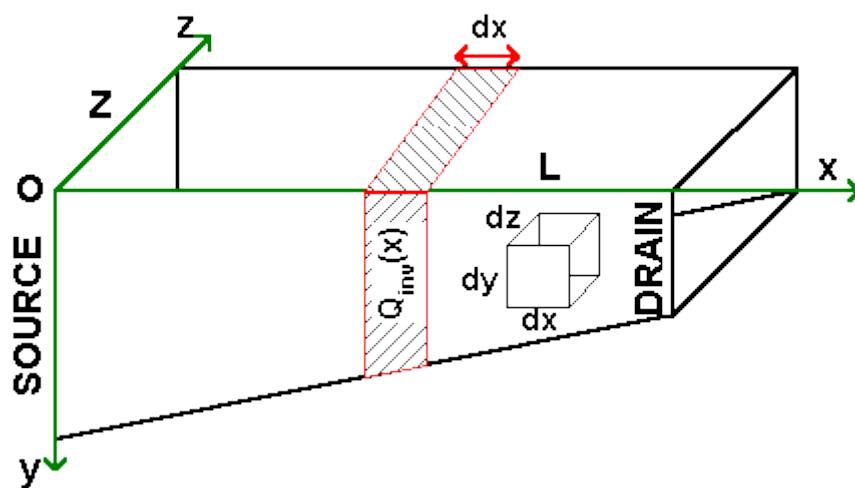

Vue "supérieure" du MOSFET étudié

- L : longueur de grille (partie de la distance entre la source et le drain recouverte par le contact de grille)

- Z : largeur de grille.

- Capacité MOS en régime de bande plate possède une couche d'inversion ( $V_{GS} > V_{TH}$ ).

- La mobilité des électrons de la couche d'inversion est constante tout le long du canal et sa valeur est  $\mu^*$  : **mobilité de surface**. Les porteurs se trouvent dans le silicium près de l'interface avec l'isolant. A cause des interactions avec la surface, leur mobilité est plus faible que celle en volume d'un facteur 2 environ ( $\mu^* \approx \mu_n/2$ ).

- la capacité MOS est en régime de Bandes Plates.

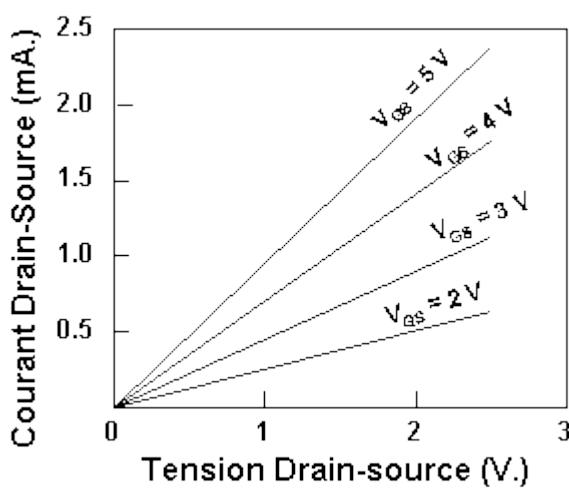

### 4.1/Modèle linéaire

On suppose que le potentiel entre le drain et la source est faible et de ce fait la charge inversion par unité de surface  $Q_{inv}$  est constante tout le long de canal.

$$I_{DS} = -\frac{Q_{inv} LZ}{t_r}$$

Le courant drain source peut s'exprimer par :

où  $t_r$  = temps de transit des porteurs entre source et drain.  $t_r = L/v$  avec  $v = \mu^* E = \mu^* V_{DS}/L$ .

$$t_r = \frac{L^2}{\mu^* V_{DS}}$$

donc :

$$I_{DS} = -\mu * Q_{inv} \frac{Z}{L} V_{DS}$$

la charge d'inversion par unité de surface est donnée par :  $Q_{inv} = -C_{inv} (V_{GS} - V_{TH})$  ou  $C_{inv}$  est la capacité d'inversion par unité de surface.

Dans le transistor E-MOS,  $C_{inv} = C_i$  : capacité de l'isolant par unité de surface car pour s'établir la charge d'inversion puise les porteurs dans les caissons de source et de drain, elle s'établit donc beaucoup plus rapidement que la charge d'inversion dans la capacité MOS. En d'autres termes, ce sont la source et le drain qui fournissent les porteurs nécessaires à la charge d'inversion.

On obtient alors :

$$I_{DS} = \mu * C_i \frac{Z}{L} (V_{GS} - V_{TH}) V_{DS}$$

Cette modélisation est valable uniquement si  $V_{DS} < V_{GS} - V_{TH}$ .

le E-MOSFET fonctionne comme une résistance commandée par une tension. On est dans la partie linéaire des caractéristiques.

## 4.2/Modèle quadratique.

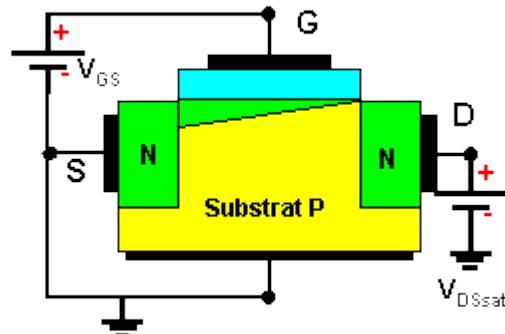

Le modèle quadratique utilise les mêmes hypothèses que le modèle linéaire mais la charge d'inversion par unité de surface n'est plus constante entre la source et le Drain, elle dépend de la position dans le canal :  $Q_{inv}(x)$ .

Par contre on ne tient pas compte de la charge d'espace, cela veut dire que dans le modèle quadratique :  $Q_{inv}(x) \gg Q_w(x)$ .

•  $V_{DS}$  est suffisant pour engendrer un potentiel local  $V(x)$  à l'interface silicium-isolant

$V(x) = 0$  pour  $x = 0$ ;  $V(x) = V_{DS}$  pour  $x = L$  : longueur de la grille.

compte tenu du sens des tensions, l'inversion est de moins en moins importante au fur et à mesure que l'on se rapproche du drain.

l'épaisseur de la couche d'inversion diminue, donc la conduction diminue selon la position entre la source et le drain.

- Pour une tension  $V_{DSsat}$ , l'inversion disparait à l'endroit du drain, on a le pincement du canal.

$$Q_{inv}(L) = 0 \text{ ce qui entraîne } dI_{DS}/dV_{DS} = 0$$

la tension  $V_{DSsat} = V_{GS} - V_{TH}$  correspond au courant  $I_{DS}$  de saturation.

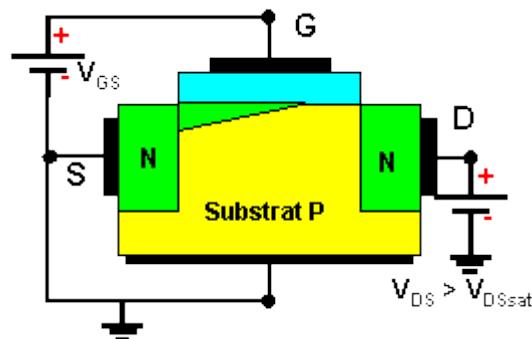

- Pour  $V_{DS} > V_{DSsat}$  le pincement du canal est obtenu dès que  $V(x) = V_{DSsat}$ , la charge d'inversion n'existe que sous une partie de la grille.

Cependant le courant  $I_{DS}$  continue à exister. Il règne un champ électrique intense entre le point de pincement  $V(x) = V_{DSsat}$  et le drain où  $V_{DS} > V_{DSsat}$ . Ce champ propulse les électrons arrivant au bout de la couche d'inversion vers le drain. L'amplitude du courant drain est donc fixée par le courant circulant de la source à la zone de pincement.

La conductivité en un point  $x$   $y$   $z$  de la couche d'inversion est :  $\sigma_{inv}(xyz) = q\mu * n_{inv}(xyz)$

Un élément de volume  $dx dy dy$  présente une conductance élémentaire :

$$d^3 g = \sigma_{inv}(xyz) \frac{dy dz}{dx} ;$$

La densité de porteurs de la couche d'inversion est constant selon Oz :  $n_{inv}(xyz) = n_{inv}$

$$d^2 g = Z q \mu * n_{inv}(xy) \frac{dy}{dx}$$

(xy) et

En intégrant la densité des porteurs sur l'épaisseur  $y_{inv}$  de la couche d'inversion à l'abscisse x on obtient :

$$\frac{dg}{dx} = Z \mu * \frac{q \int_0^{y_{inv}} n_{inv}(xy) dy}{dx}$$

$$q \int_0^{y_{inv}} n_{inv}(xy) dy = -Q_{inv}(x)$$

La conductance élémentaire d'une tranche  $dx$  de la couche d'inversion située à l'abscisse x et s'étendant sur toute la largeur Z du canal est donc :

$$\frac{dg}{dx} = -Z \mu * \frac{Q_{inv}(x)}{dx}$$

Cette élément de canal parcouru par le courant  $I_{DS}$  présente à ses borne une différence de

$$I_{DS} = \frac{dg}{dx} dV(x)$$

potentiel  $dV(x)$  telle que : . soit :

$$I_{DS} dx = -Z \mu * Q_{inv}(x) dV(x)$$

En négligeant la contribution de la ZCE on peut poser :

$$Q_{inv}(x) = -C_{inv} (V_{GS} - V_{TH} - V(x))$$

ce qui mène à :

$$I_{DS} dx = -Z \mu * Q_{inv}(x) dV(x)$$

lorsque x varie de 0 à L, longueur du canal,  $V(x)$  varie de  $V_S = 0$  à  $V_{DS}$  donc en intégrant sur x :

$$I_{DS} \int_0^L dx = Z \mu * C_i \int_0^{V_{DS}} (V_{GS} - V_{TH} - V(x)) dV(x)$$

Soit :

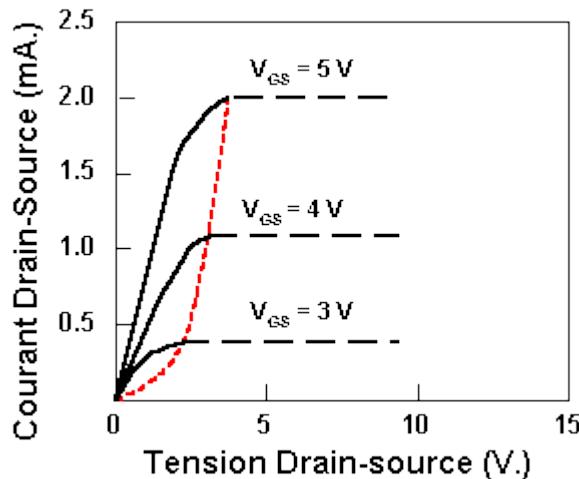

$$I_{DS} = \mu * C_i \frac{Z}{L} \left[ (V_{GS} - V_{TH}) V_{DS} - \frac{V_{DS}^2}{2} \right] \text{ (mA)}$$

Le courant  $I_{DS}$  croît d'abord linéairement en fonction de la tension  $V_{DS}$  puis atteint une valeur maximum quand  $V_{DS} = V_{GS} - V_{TH}$  : **le courant de saturation** tel que :

$$I_{DSsat} = \mu * C_i \frac{Z}{L} \frac{(V_{GS} - V_{TH})^2}{2} \text{ (mA)}$$

ensuite pour les tensions  $V_{DS}$  supérieures, le modèle précédent n'est plus valable, le courant reste constant à la valeur de saturation

## 5/Régimes de fonctionnement

On remarque que ce réseau de caractéristiques comporte trois régions :

- La région de blocage (cut off) pour  $V_{GS} < V_{TH}$

- La région de fonctionnement en triode (appelée ainsi par similitude avec les caractéristiques d'un tube triode) ou bien région linéaire correspondant à un fonctionnement du canal avant pincement.

- La région dite « de saturation du courant drain » correspondant à un fonctionnement "pincé" dans cette zone de fonctionnement, le courant drain est indépendant de la tension drain-source  $V_{DS}$  et suit la tension grille-source  $V_{GS}$  selon une loi quadratique.

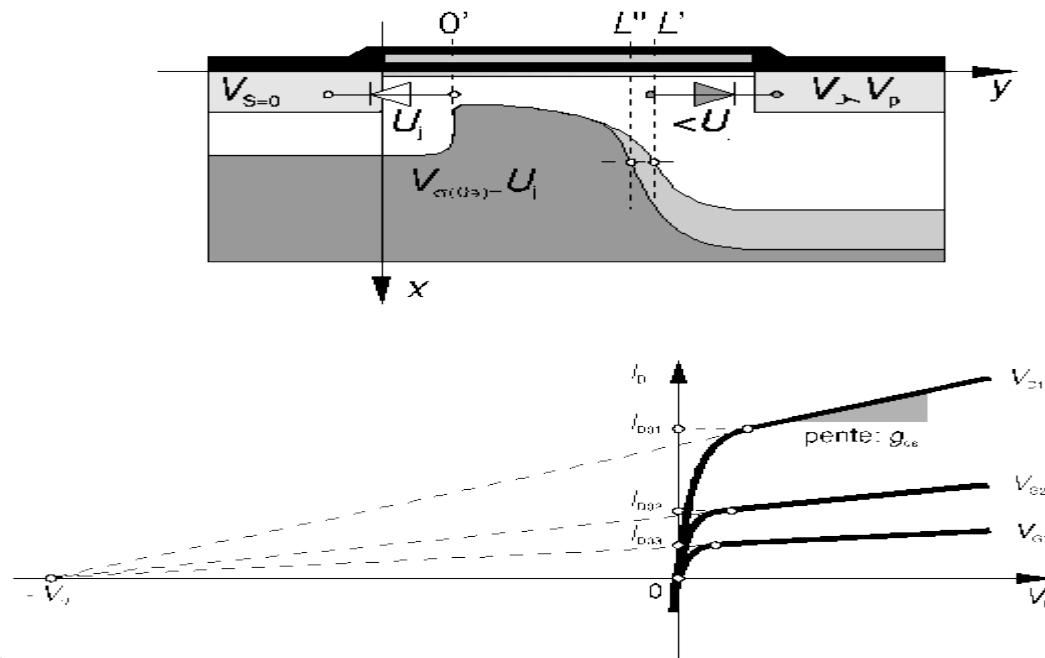

## 6/ Modulation de la longueur du canal

On a admis que le transistor MOS se comportait comme une source de courant idéale en régime de saturation. En réalité, l'extrémité effective  $L'$  du canal varie en fonction du potentiel de drain que l'on applique et on admet qu'en tenant compte de l'effet de modulation de la longueur du canal, le courant de drain s'écrit:

$$I_D \cong I_{D0} \left( 1 + \frac{V_D}{V_M} \right) = I_{D0} (1 + \lambda V_D)$$

$\lambda$  et  $V_M$  sont indifféremment appelés paramètres de modulation de la longueur du canal. La figure montre des caractéristiques de sortie du transistor MOS qui tiennent compte de la modulation de la longueur du CANAL

Effet de la modulation de la longueur du canal

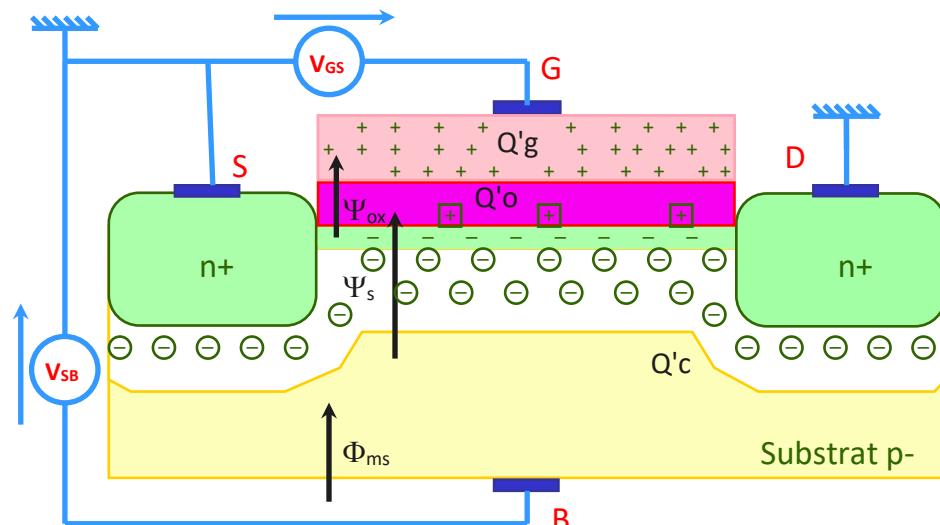

## 7/Effet de substrat (Body Effect)

S'il y a inversion avec  $V_{SB} = 0$  et que  $V_{SB}$  devient brusquement positif, les électrons du canal vont s'en aller par S vers B       $\rightarrow$     inversion diminuée.

Pour maintenir la même inversion, il faut donc lutter contre  $V_{SB}$

$Q'c$  : charges présentes à l'interface sous l'oxyde

$Q'o$  : charges parasites piégées dans l'oxyde à l'interface (fixes)

$Q'g$  : charges présentes au niveau de la grille

$\Psi_{ox}$  : potentiel aux bornes de l'oxyde

$\Psi_s$  : potentiel entre la surface et le cœur du substrat

$\Phi_{ms}$ : potentiel de contact (Cte)

$Q'b$  : charges fixes présentes en surface

$Q'i$  : charges mobiles présentes en surface

$$Q'c = Q'b + Q'i$$

Les charges sont comptées par unité de surface

En forte inversion, on aura donc :  $\Psi_s = \Phi_B + V_{SB}$

$$\text{Soit } Q'_b = -\sqrt{2q\varepsilon_r\varepsilon_0N_A} \sqrt{\Phi_B + V_{SB}} = -\gamma C'_{ox} \sqrt{\Phi_B + V_{SB}}$$

$$\text{Or } V_{GB} = \Psi_s + \Phi_{ms} + \Psi_{ox} \text{ et } \Psi_{ox} = \frac{Q'_G}{C'_{ox}} = \frac{-Q'_o - Q'_i - Q'_b}{C'_{ox}}$$

$$\text{Alors } V_{GB} = V_{FB} + \Phi_B + V_{SB} - \frac{Q'_i}{C'_{ox}} - \frac{Q'_b}{C'_{ox}}$$

$$\text{D'où : } Q'_i = -C'_{ox} (V_{GB} - V_{SB} - \Phi_B - V_{FB} - \gamma \sqrt{\Phi_B + V_{SB}})$$

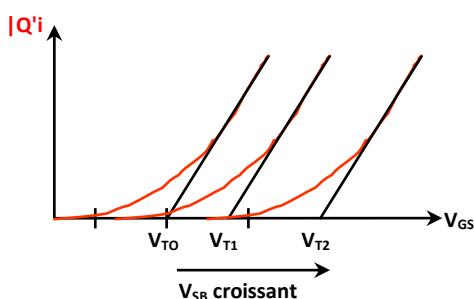

$$Q'_i = -C'_{ox} (V_{GS} - V_{TO} - \gamma \sqrt{\Phi_B + V_{SB}} + \gamma \sqrt{\Phi_B})$$

$$\text{Soit } Q'_i = -C'_{ox} (V_{GS} - V_{TH})$$

$$\text{Avec } V_{TH} = V_{TO} + \gamma (\sqrt{\Phi_B + V_{SB}} - \sqrt{\Phi_B})$$

## 8/Influence de la température

---

Les paramètres K et  $V_{TH}$  sont dépendants de la température :

La tension de seuil  $V_{TH}$  décroît d'environ 2mV par degré d'élévation de température.

Le paramètre K décroît avec la température et son effet est prédominant.

Il en résulte que le courant Drain  $I_D$  décroît lorsque la température s'élève. Ce résultat est particulièrement important pour les MOSFET de puissance.

## 9/Effet de champ électrique

---

Lorsqu'on augmente la tension Drain-Source  $V_{DS}$ , le champ électrique à la jonction PN Drain Substrat (qui est relié à la source) s'élève, et on atteint la tension d'avalanche.

Pour éviter d'atteindre ce phénomène dangereux pour le composant, le constructeur spécifie la tension Drain-Source maximale à ne pas dépasser.

Afin d'éviter l'accumulation de charges statiques dans le condensateur grille-substrat qui pourraient provoquer un perçage de l'oxyde extrêmement fin servant de diélectrique, des diodes de protection intégrées limitent la tension grille-source. La tension maximale grille-source  $V_{GSmax}$  est spécifiée par le constructeur.

## 10/Modèle Pspice et simulation du transistor MOS

---

Le modèle SPICE d'un MOSFET comprend une variété d'éléments de circuit parasite et certains paramètres liés au processus de fabrication en plus des éléments précédemment discutés dans ce chapitre. La syntaxe d'un MOSFET intègre les paramètres qu'un concepteur de circuits peut contrôler:

### **syntaxe du MOSFET**

```

M <nom> <nœud drain> <nœud grille> <nœud source> <nœud substrat>

+ [L=][W=][AD=][AS=]

+ [PD=][PS=][NRD=][NRS=]

+ [NRG=][NRB=]

```

Où L est la longueur de la grille, W est la largeur de la grille, AD zone du drain, AS zone de la source

PD est le périmètre drain, PS est le périmètre source

### **Example:**

M1 3 2 1 0 NMOS L=1u W=6u

```

.MODEL NFET NMOS (LEVEL=2 L=1u W=1u VTO=-1.44 KP=8.64E-6

+ NSUB=1E17 TOX=20n)

```

où M1 est un transistor spécifique dans le circuit, tandis que le modèle de transistor "NFET" utilise le modèle intégré NFET pour spécifier les paramètres liés au processus et à la technologie du MOSFET. Une liste des paramètres SPICE sélectionnés et leur relation avec les paramètres discutés dans ce texte est fournie dans le tableau ci-dessous.

| SPICE variable | Equation                                                                        |

|----------------|---------------------------------------------------------------------------------|

| TOX            | $TOX = t_{ox}$                                                                  |

| KP             | $KP = \mu C_{ox}$                                                               |

| VTO            | $VTO = V_{FB} + 2\phi_F + \frac{\sqrt{2\varepsilon_3 q N_a (2\phi_F)}}{C_{OX}}$ |

| GAMMA          | $GAMMA = \gamma = \frac{\sqrt{2\varepsilon_3 q N_a}}{C_{OX}}$                   |

| NSUB           | $NSUB = N_d \text{ or } N_a$                                                    |

| U0             | $U0 = \mu$                                                                      |

| LAMBDA         | $LAMBDA = \lambda$                                                              |

| VMAX           | $VMAX = v_{sat}$                                                                |

#### Paramètres SPICE et équations correspondantes

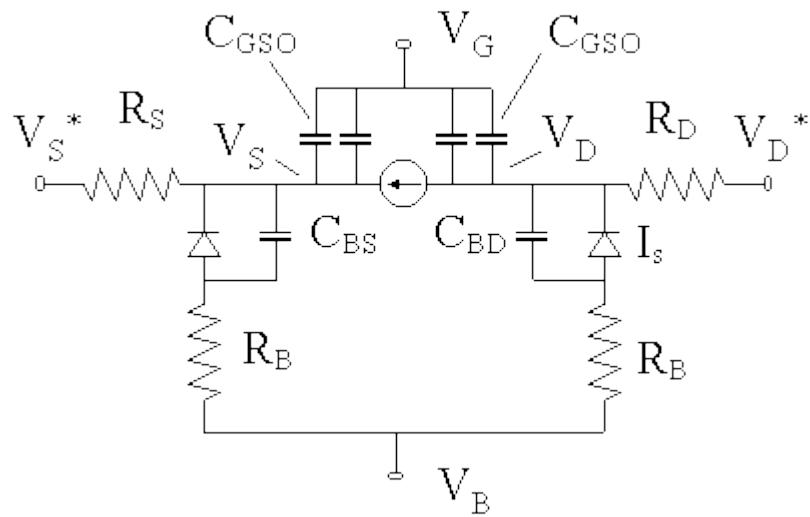

De plus, il existe des paramètres supplémentaires, qui peuvent être spécifiés pour améliorer encore la précision du modèle, tels que:

LD, diffusion latérale (longueur)

RD, résistance ohmique du drain

RG, résistance ohmique de la grille

IS, courant de saturation p-n du substrat

CBD, capacité p-n à polarisation substrat et drain à la masse

CGSO / CGDO, capacité de chevauchement grille-source / drain / largeur de canal

XJ, profondeur de la jonction métallurgique

WD, diffusion latérale (largeur)

RS, résistance ohmique de la source

RB, résistance ohmique du substrat

JS, courant de saturation p-n dans le substrat

CBS, capacité p-n à polarisation substrat et grille à la masse

La capacité de chevauchement grille-source / grille-drain par largeur de canal est obtenue à partir de:

$$C_{GSO} = C_{GDO} = \frac{\epsilon_{ox} \Delta L}{t_{ox}}$$

Où  $\Delta L$  est le chevauchement entre la grille et la région source ou drain. Le circuit équivalent correspondant est fourni par la figure ci-dessous :

modèle large signal d'un MOSFET

SPICE permet également à l'utilisateur de choisir d'autres modèles MOSFET plus détaillés en sélectionnant le modèle LEVEL.