**MIC28 «TP Conception Cls Numériques»**

***TP N° 2***

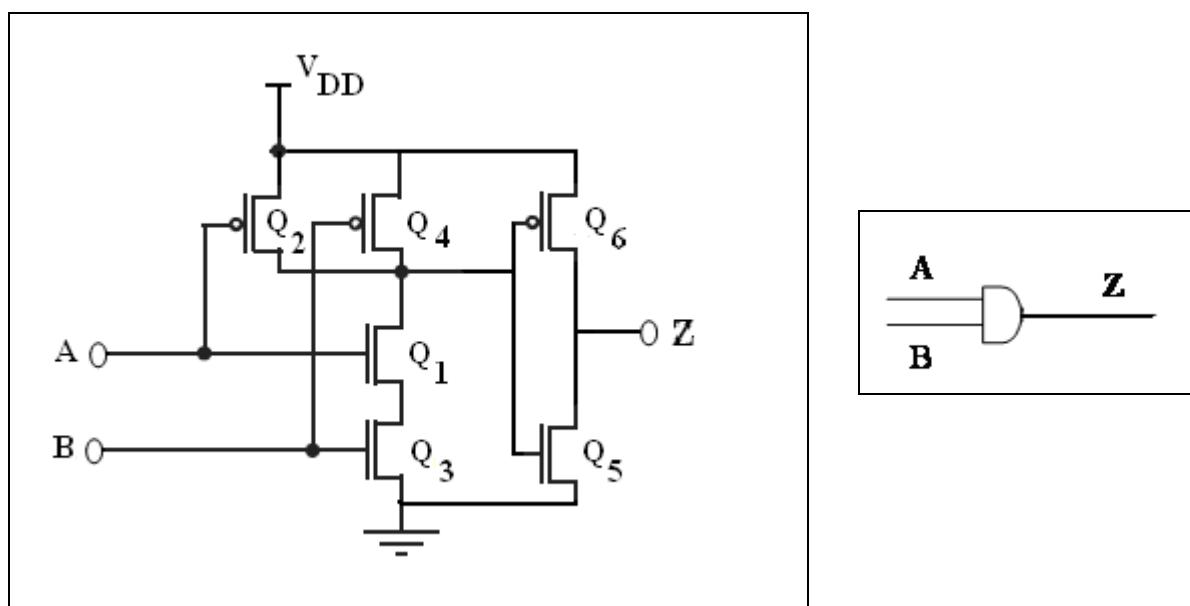

***Porte AND CMOS à deux entrées***

On se propose de simuler une porte AND (ET) à 2 entrées A et B en technologie CMOS dont le schéma électrique et la table de vérité sont donnés par les figures ci-dessus.

| <b>A</b> | <b>B</b> | <b>Q<sub>1</sub></b> | <b>Q<sub>2</sub></b> | <b>Q<sub>3</sub></b> | <b>Q<sub>4</sub></b> | <b>Q<sub>5</sub></b> | <b>Q<sub>6</sub></b> | <b>Z</b> |

|----------|----------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------|

| L        | L        | OFF                  | ON                   | OFF                  | ON                   | ON                   | OFF                  | <b>L</b> |

| L        | H        | OFF                  | ON                   | ON                   | OFF                  | ON                   | OFF                  | <b>L</b> |

| H        | L        | ON                   | OFF                  | OFF                  | ON                   | OFF                  | ON                   | <b>L</b> |

| H        | H        | ON                   | OFF                  | ON                   | OFF                  | OFF                  | ON                   | <b>H</b> |

Tracer, sur le même graphe, les tensions d'entrée A et B ainsi que la tension de sortie Z.