## Chapitre5

### La boucle à verrouillage de phase (PLL)

#### 5.1. Principe de la boucle à verrouillage de phase

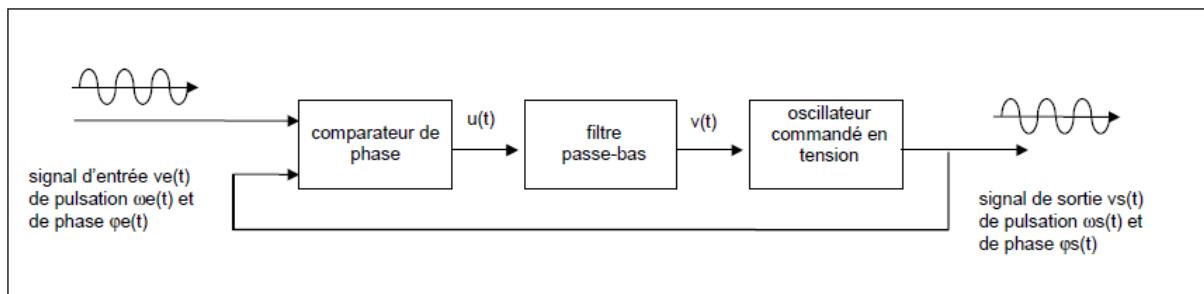

La boucle à verrouillage de phase : Phase Locked Loop (PLL), permet d'asservir la fréquence d'un VCO à la fréquence d'un signal de référence dans une certaine plage autour de la fréquence centrale  $f_0$

**Figure 1.** Structure de base de la boucle à verrouillage de phase

Les éléments de la PLL sont les suivants :

l'oscillateur VCO donne une fréquence qui varie en fonction de la tension de commande  $v$  appliquée sur son entrée. Il est linéarisé autour de  $f_0$  et caractérisé par sa pente  $K_0$

$$K_0 = \frac{\text{variation de la pulsation du signal de sortie}}{\text{variation de la tension de commande}} \quad \text{en radian/s/V}$$

la fréquence du VCO est comparée avec une fréquence de référence ( consigne ) grâce à un comparateur de phase ( Ou exclusif, comparateur phase-fréquence, pompe de charge ) le comparateur de phase fournit à sa sortie une tension  $u$  alternative dont la valeur moyenne  $v$  donnée par un passe-bas est proportionnelle au déphasage entre  $ve$  et  $vs$  . Il est caractérisé par un coefficient souvent noté  $K_d$  défini par :

$$K_d = \frac{\text{valeur moyenne de la tension en sortie}}{\text{déphasage entre les signaux d'entrée}} = \frac{U_{\text{moyen}}}{\phi} \quad \text{en volts/radian}$$

Le fonctionnement de la PLL est le suivant :

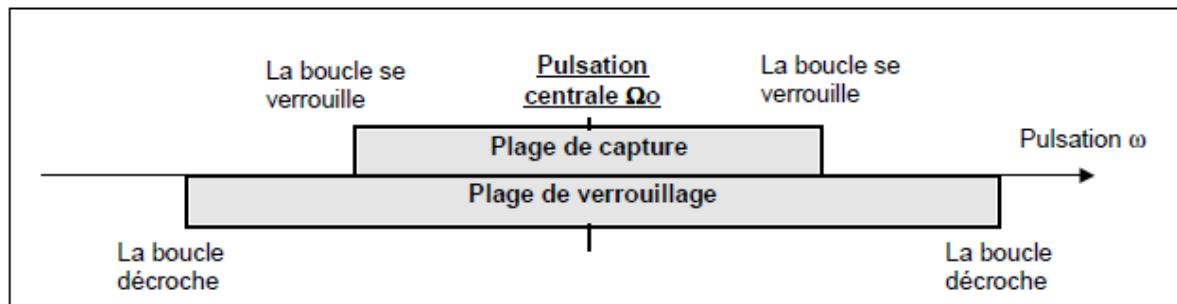

en l'absence de signal injecté à l'entrée de la boucle, ou si la fréquence du signal injecté est en dehors de la plage de fonctionnement du VCO, la boucle est dite non verrouillée et  $f_s = f_0$

⇒ si on injecte dans la boucle un signal de fréquence  $f_e$  voisin de  $f_0$ , la PLL se verrouille et on aboutit

au bout d'un temps bref ( 1 à 100 ms en général) à un état stable caractérisé par  $f_s = f_e$

⇒ une fois la boucle verrouillée ou accrochée, la fréquence d'entrée peut varier dans la plage de verrouillage sans que cette boucle ne décroche et on a toujours  $f_s = f_e$

⇒ si la fréquence d'entrée sort de la plage de verrouillage, la boucle décroche et on revient à la situation d'une boucle non verrouillée (à éviter dans la pratique !)

Figure 2. Les plages de capture et de verrouillage.

Pour raccrocher la boucle, il faut alors revenir au voisinage de  $f_0$  et pénétrer dans la plage de capture

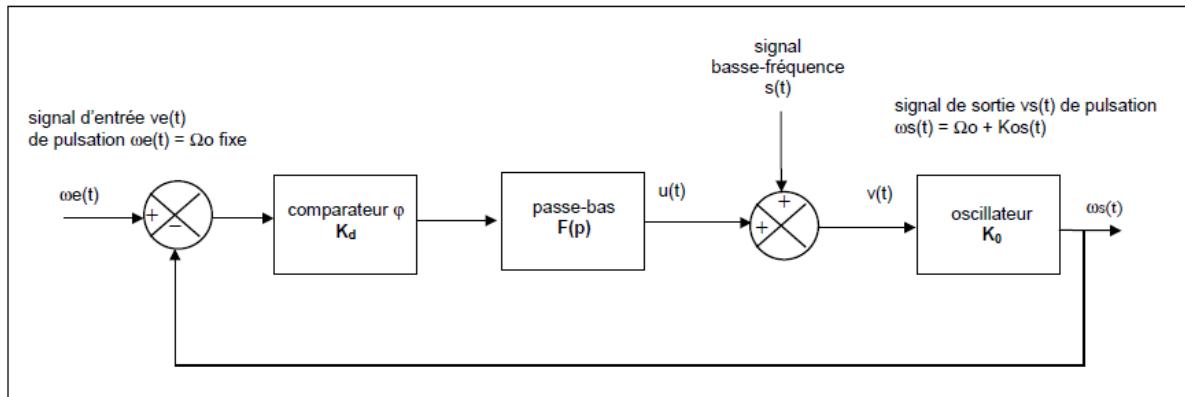

### 5.2. Applications en modulation de fréquence :

la production d'un signal FM se heurte à deux exigences contradictoires à savoir :

- bonne stabilité de la porteuse  $f_0$

- excursion en fréquence autour de  $f_0$  suffisante

La boucle à verrouillage de phase permet d'atteindre ces 2 objectifs simultanément :

Figure 3. Modulateur de fréquence à PLL.

Le fonctionnement est le suivant :

la PLL est accrochée sur un oscillateur à quartz fournissant un signal de fréquence  $F_0$

- le signal modulant est superposé au signal de commande  $v$  à l'entrée du VCO

- la fréquence de coupure  $f_c$  du filtre passe-bas sera choisie très basse, par exemple

$$f_c = 0,1 \text{ Hz}$$

La boucle est alors efficace vis-à-vis des dérives lentes du VCO, mais incapable de réagir devant des variations rapides de la fréquence de sortie causées par le signal modulant.

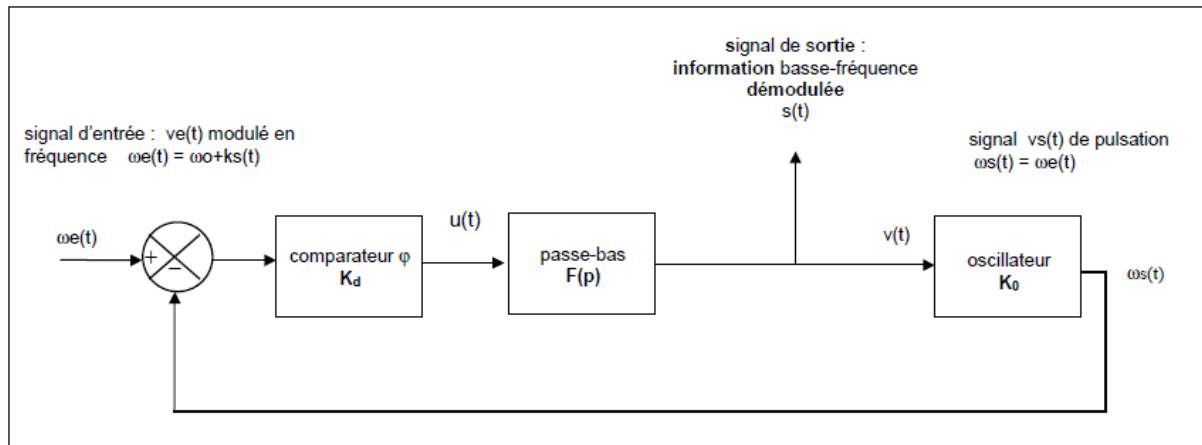

⇒ La démodulation FM peut aussi se réaliser simplement à l'aide d'une PLL. La sortie utile de cette structure se trouve alors à l'entrée du VCO :

**Figure 4.** Démodulateur de fréquence à PLL.

Pour un signal modulé en fréquence, l'erreur n'est sauf cas particulier pas nulle, mais reste faible pour une boucle dont le filtre est bien calculé.

La fréquence de sortie suit donc d'assez près la fréquence d'entrée, et la tension à l'entrée du VCO variera donc comme la fréquence. On récupère donc à l'entrée du VCO une image assez fidèle du signal modulant.